Intel 4004 processor | |

| General information | |

|---|---|

| Launched | November 15, 1971 |

| Discontinued | 1981[1] |

| Marketed by | Intel |

| Designed by | Intel |

| Common manufacturer(s) |

|

| Performance | |

| Max. CPU clock rate | 740 KHz to 750 KHz |

| Data width | 4 bits |

| Address width | 12 bits (multiplexed) |

| Architecture and classification | |

| Application | Busicom calculator, arithmetic manipulation |

| Technology node | 10 μm |

| Instruction set | 4-bit BCD-oriented |

| Physical specifications | |

| Transistors |

|

| Package(s) |

|

| Socket(s) | |

| History | |

| Successor(s) | Intel 8008 (8-bit) Intel 4040 (4-bit) |

| Support status | |

| Unsupported | |

The Intel 4004 is a 4-bit central processing unit (CPU) released by Intel Corporation in 1971. Sold for US$60 (equivalent to $430 in 2022,[2] $449.43 in 2023[3]), it was the first commercially produced microprocessor,[4] and the first in a long line of Intel CPUs.

The 4004 was the first significant example of large-scale integration, showcasing the superiority of the MOS silicon gate technology (SGT). Compared to the incumbent technology, the SGT integrated on the same chip area twice the number of transistors with five times the operating speed. This step-function increase in performance made possible a single-chip CPU, replacing the existing multi-chip CPUs. The innovative 4004 chip design served as a model on how to use the SGT for complex logic and memory circuits, thus accelerating the adoption of the SGT by the world’s semiconductor industry. The developer of the original SGT at Fairchild was Federico Faggin, who designed the first commercial integrated circuit (IC) that used the new technology, proving its superiority for analog/digital applications (Fairchild 3708 in 1968). He later used the SGT at Intel to obtain the unprecedented integration necessary to make the 4004.

The project traces its history to 1969, when Busicom Corp. approached Intel to design a family of seven chips for an electronic calculator, three of which constituted a CPU specialized for making different calculating machines. The CPU was based on data stored on shift-registers and instructions stored on ROM (read only memory). The complexity of the three-chip CPU logic design led Marcian Hoff to propose a more conventional CPU architecture based on data stored on RAM (random-access memory). This architecture was much simpler and more general-purpose and could potentially be integrated into a single chip, thus reducing the cost and improving the speed. Design began in April 1970 under the direction of Faggin, aided by Masatoshi Shima, who contributed to the architecture and later to the logic design. The first delivery of a fully operational 4004 was in March 1971 to Busicom for its 141-PF printing calculator engineering prototype (now displayed in the Computer History Museum in Mountain View, California).[5] General sales began July 1971.

A number of innovations developed by Faggin while working at Fairchild Semiconductor allowed the 4004 to be produced on a single chip. The main concept was the use of the self-aligned gate, made of polysilicon rather than metal, which allowed the components to be much closer together and work at higher speed. To make the 4004 possible, Faggin also developed the "bootstrap load", considered unfeasible with silicon gate, and the "buried contact" that allowed the silicon gates to be connected directly to the source and drain of the transistors without the use of metal. Together, these innovations doubled the circuit density, and thus halved cost, allowing a single chip to contain 2,300 transistors and run five times faster than designs using the previous MOS technology with aluminum gates.

The 4004 design was later improved by Faggin as the Intel 4040 in 1974. The Intel 8008 and 8080 were unrelated designs in spite of the similar naming.

History

Original concept

In April 1969, Busicom approached Intel to produce a new design for an electronic calculator. They based their design on the architecture of the 1965 Olivetti Programma 101, one of the world's first tabletop programmable calculators.[6][7] The key difference was that the Busicom design would use integrated circuits to replace the printed circuit boards filled with individual components, and solid-state shift registers for memory instead of the costly magnetostriction wire in the 101.

In contrast to earlier calculator designs, Busicom had developed a general-purpose processor concept with the goal of introducing it in a low-end desktop printing calculator, and then using the same design for other roles like cash registers and automatic teller machines. The company had already produced a calculator using TTL small-scale integration logic ICs and were interested in having Intel reduce the chip count using Intel's medium-scale integration (MSI) techniques.[8]

Intel assigned the recently hired Marcian Hoff, employee number 12, to act as the liaison between the two companies. In late June, three engineers from Busicom, Masatoshi Shima and his colleagues Masuda and Takayama, traveled to Intel to introduce the design. Although he had only been assigned to liaise with the engineers, Hoff began studying the concept. Their initial proposal had seven ICs: program control, arithmetic unit (ALU), timing, program ROM, shift registers for temporary memory, printer controller and input/output control.[9]

Hoff became concerned that the number of chips and the required interconnections between them would make Busicom's price goals impossible to meet. Combining the chips would reduce the complexity and cost. He was also concerned that the still-small Intel would not have enough design staff to make seven separate chips at the same time. He raised these concerns with upper management, and Bob Noyce, the CEO, told Hoff he would support a different approach if it seemed feasible.[9]

Simplified design

A key concept in the Busicom design was that the program control and ALU were not aimed specifically at the calculator market, it was the program in ROM that turned it into a calculator. The original idea was that the company could use the same chips with different amounts of shift-register RAM and program ROM to produce a range of calculating machines. Hoff was struck by how closely the Busicom's instruction set architecture matched that of general-purpose computers. He began to consider whether a truly general-purpose processor could be made cheaply enough to be used in a calculator.[10] When later asked where he got the ideas for the architecture of the first microprocessor, Hoff related that Plessey, "a British tractor company",[11] had donated a minicomputer to Stanford, and he had "played with it some" while he was there. Tadashi Sasaki attributes the idea to break the calculator into four parts to an unnamed woman from the Nara Women's College present at a brainstorming meeting that was held in Japan prior to his first meeting with Intel.[12]

Another development that allowed this design to be made practical was Intel's work on the earliest dynamic RAM (DRAM) chips. Shift registers at that time were among the only low-cost read and write memory devices. They do not allow random access, instead, with every clock pulse they move the stored data one cell along a chain of cells. The time to retrieve any given data, one byte for instance, is a function of the clock speed and the number of cells in a chain. If the processor had to wait for each bit to cycle through the register, the resulting effective speed would be far too low to be practical. DRAM, on the other hand, allowed random access to any data they stored, while also having roughly double the capacity and thus being less expensive.[10]

Finally, Hoff noticed that much of the complexity of the program control chip was due to every instruction being implemented separately. He suggested that the chip instead support subroutine calls and instructions be implemented as subroutines where possible. The application naturally suggested a 4-bit design, as this allowed direct manipulation of binary-coded decimal (BCD) values used by calculators. Hoff worked on the overall design concept through July and August 1969 but found that the Busicom executives seemed uninterested in his proposal.[10]

Mazor joins

Unknown to Hoff, the Busicom team were extremely interested in his proposal. However, there were a number of specific issues that they were concerned about. One key issue was that certain routines like decimal adjust and keyboard handling would use large amounts of ROM space if implemented as subroutines. Another was that the design did not feature any sort of interrupt, so dealing with real-time events would be difficult. Finally, storing the numbers as 4-bit BCD would require additional memory to store the sign and decimal place.[13]

In September 1969, Stanley Mazor joined Intel from Fairchild. Hoff and Mazor quickly came up with solutions to the Busicom concerns. To address the complexity of the subroutines, originally solved in Busicom's design using one-byte macroinstructions and complex decoder circuitry, Mazor developed a 20-byte long interpreter that executed the same macroinstructions. Shima suggested adding a new interrupt that would be triggered by a pin, thereby allowing the keyboard to be interrupt-driven. He also modified the Branch Back (return from subroutine) instruction to clear the accumulator.[14]

To reach the price goals, it was important that the chip be as small as possible and use the fewest number of leads. As data was 4 bits and the address space was 12 bits (4096 bytes), there was no way direct access could be arranged with anything fewer than about 24 pins. This was not small enough, so the design would use a 16-pin dual in-line package (DIP) layout and use multiplexing of a single set of 4 lines. This meant specifying which address in ROM to access required three clock cycles, and another two to read it from memory. Running at 1 MHz would allow it to perform math on the BCD values at about 80 microseconds per digit.[15]

The result of the discussions between Intel and Busicom was an architecture that reduced the 7-chip Busicom design to a 4-chip Intel proposal composed of CPU, ROM, RAM and I/O (input-output) devices. The proposal was presented to a visiting team of Busicom executives in October 1969. They agreed that the new concept was superior and gave Intel the go-ahead to begin development. Hoff was upset to learn that the contract assigned all rights to the design to Busicom, in spite of it being designed entirely within Intel. The team then left for Japan, but Shima remained in California until December, developing many of the subroutines.[15]

Faggin joins

Neither Hoff nor Mazor, who worked in the Applications Research group, had experience designing the actual silicon, and the design group was already overworked with the development of memory devices. In April 1970, Leslie Vadász, who ran the MOS design group, hired Federico Faggin from Fairchild Semiconductor to take over the project.[16] Faggin had already made a name for himself by leading the entire development of the MOS silicon gate technology and the design of the first commercial integrated circuit (IC) made with it. The new technology was going to change the entire semiconductor market.

Integrated circuits consist of a number of individual components like transistors and resistors that are produced by mixing the underlying silicon with "dopants". This is normally accomplished by heating the chip in the presence of a chemical gas, which diffuses into the surface. Previously, the individual components were connected together to make a circuit using aluminum wires deposited on the surface. As aluminum melts at 600 degrees and silicon at 1000, the traces typically had to be deposited as the last step, which often complicated the production cycle.

In 1967, Bell Labs released a paper about making MOS transistors with self-aligned gates made of silicon rather than metal. These devices, however, were a proof-of-concept and could not be used to make ICs. Faggin and Tom Klein had taken what was a curiosity and developed the entire process technology needed to fabricate reliable ICs. Faggin also designed and produced the Fairchild 3708,[17] the first IC made with SGT, first sold at the end of 1968, and featured on the cover of Electronics in September 1969.[18][16] The silicon gate technology also reduced the leakage current by more than 100 times, making possible sophisticated dynamic circuits like DRAMs (dynamic random access memories). It also allowed the highly-doped silicon used for the gates to form the interconnections, greatly improving the circuit density of random-logic ICs like microprocessors.

This technique meant the interconnections could be performed at any time in the process. More importantly, the wiring was deposited using the same equipment that made the rest of the components. This meant that the slight differences in layout between different machine types was eliminated. Previously the interconnects had to be much larger than required in order to ensure the aluminum touched the silicon components which would be offset due to inaccuracies in the machinery. With this issue eliminated, the circuits could be placed much closer together, immediately doubling the density of the components, and thus reducing their cost by the same amount. Additionally, the aluminum wiring acted as capacitors which limited the signal speed; removing these allowed the chips to run at faster speeds.[19][20]

At Intel, Faggin began design of the new processor using this self-aligned gate process. Only days after Faggin joined the company Intel, Shima arrived from Japan. He was disappointed to learn that no work on the project had taken place since he left in December, and expressed his concern original schedule was now impossible. Faggin responded by working well into the night every day, and Shima stayed on for another six months to help. Faggin himself immersed himself in workweeks that spanned 70 to 80 hours.[21] Additional advances were needed to reach the required circuit density. One of these advances was the use of "buried contacts"[22][23] that allowed the silicon connecting wires to be directly connected to the components. Another was figuring out how to make adding "bootstrap loads" with silicon gate as part of one of the masking steps,[24] eliminating one step from the processing.[16] Without these two innovations by Faggin, Hoff’s architecture could not have been realized in a single chip.

Into production

Intel's chip-naming scheme at that time used a four-digit number for each component. The first digit indicated the process technology used, the second digit indicated the generic function, and the last two digits specified the sequential number in the development of that component type. Using this convention, the chips would have been known as the 1302, 1105, 1507, and 1202. Faggin felt this would obscure the fact that they formed a coherent set, and decided to name them as the "4000 family".[25] The four chips were the following: the 4001, 256-byte 4-bit ROM; the 4002, DRAM with four 20-nibble registers; the 4003, I/O with a 10-bit static shift register with serial and parallel outputs; and the 4004 CPU. A fully expanded system could support 16 4001's for a total of 4 kB of ROM, 16 4002's for a total of 1,280 nibbles (640 bytes) of RAM, and an unlimited number of 4003's. The 4003's were connected to programmable input and output pins on the 4001 and to output pins on the 4002, not directly to the CPU.[9]

With the design complete, Shima returned to Japan to begin building a prototype of the calculator. The first wafers of the 4001 were processed in October 1970,[16] followed by the 4003 and 4002 in November. The 4002 proved to have a minor problem that was easily corrected. The first 4004s arrived at the end of December, and were completely non-functional. Probing the chip, Faggin found that the buried-contact fabrication step had been left out. A second run was fabricated in January 1971 and the 4004 worked perfectly except for two minor problems.

Faggin was sending samples of these chips to Shima as they arrived. In April, they learned the calculator prototype was operational. Later that month, Shima sent Intel the final masks for the 4001 ROMs, the design was now complete. It consisted of one 4004, two 4002, three 4003, and four 4001 chips. An additional 4001 supplied the optional square root function. One final change was added after Faggin found a frustrating problem in the 4001 that only occurred when the chips were hot. Adding a new register decoder circuit was Faggin's solution. The same problem was also seen in the 4002 and the same solution was used. Production began in quantity in August 1971.[26]

Marketing the 4004

During a call to Shima, Faggin learned that Busicom was in financial difficulty and would likely fail if the chip price was not reduced. Faggin then convinced Noyce to lower the price in exchange for releasing Intel from the exclusivity agreement. In May 1971 Busicom agreed to this, on the condition that it not be used for any other calculator project and that Intel would repay their $60,000 development costs.[26] With this change of marketing focus name of the chip family name was changed to MCS-4, short for Micro Computer System, 4-bit.[25]

Intel management was skeptical that their sales team could explain the product to their customers. As Intel was now successful in the memory market, they were concerned the 4004 might confuse the market and were hesitant to advertise it.[26] They feared current Intel customers might view the new product as competition, purchasing memory from competitors instead.[27] Hoff and Mazor were also concerned that the design's limitations would make it less interesting to users who were accustomed to the new 16-bit minicomputers entering the market at that time.[28]

This all changed in the summer of 1971, when Ed Gelbach, formerly of Texas Instruments, took over the marketing department and immediately began plans to publicly announce the product.[28] This took place in the November 1971 when Intel ran ads "Announcing a new era of integrated electronics,"[29] first appearing in the November 15 edition of Electronic News.[30]

The 8008

The 4004 became the first commercial microprocessor available for general use.[lower-alpha 1] This was almost not the case.[28]

In December 1969, Intel was approached by Computer Terminal Corporation (CTC) to produce a custom bipolar memory chip for a computer terminal they were designing, the Datapoint 2200. Mazor and Hoff considered their CPU design and concluded it was not much more complicated than the 4004, and that it could be implemented as a single-chip 8-bit CPU.[15] A few weeks before they hired Faggin, in March 1970 Intel hired Hal Feeney to design the 8008, at that time called 1201 following Intel's naming convention. However, CTC decided to initially proceed with a conventional TTL implementation of their CPU and the project was lowered in priority. Feeney was assigned to other projects and ultimately ended up helping Faggin with testing the 4000 family chips.[31]

In January 1971, Feeney was reassigned back to the 1201 under Faggin’s supervision and production chips were available in March 1972. In May, Hoff and Mazor went on a speaking tour to introduce the two CPU designs around the USA. The tradeoffs between the two designs were that with the 4004 and its memory and I/O chips it was much easier to build a complete computer system while the 8008 was more flexible, had a larger 16 kB address space, and offered more instructions. A significant difference is that while a minimal 4004 system could be built using only two chips, one 4004 and one 4001 (256-byte ROM), the 8008 would require at least 20 additional TTL components for interfacing with memory and I/O functions[31]

The two designs found themselves being used in different roles. The 4004 was used where the cost of implementation was the major concern, and became widely used in embedded controllers for applications like microwave ovens or traffic lights and similar roles. The 8008 instead found itself mostly used in user-programmable applications, such as computer terminals, microcomputers and similar roles. This split in functionality remains to this day, with the former being known as a microcontroller.[31]

Contemporaneous CPU chips

Three other CPU chip designs were produced at about the same time: the Four-Phase Systems AL1, done in 1969; the MP944, completed in 1970 and used in the F-14 Tomcat fighter jet; and the Texas Instruments TMS-0100 chip, announced on September 17, 1971. The MP944 was a collection of six chips forming a single processor unit. The TMS0100 chip was presented as a "calculator on a chip" with the original designation TMS1802NC.[32] This chip contains a very primitive CPU and can only be used to implement various simple four-function calculators. It is the precursor of the TMS1000, introduced in 1974, which is considered the first microcontroller—i.e., a computer on a chip containing not only the CPU, but also ROM, RAM, and I/O functions.[33] The MCS-4 family of four chips developed by Intel, of which the 4004 is the CPU or microprocessor, was far more versatile and powerful than the single-chip TMS1000, allowing the creation of a variety of small computers for various applications.

Zilog, the first company entirely dedicated to microprocessors and microcontrollers, was started by Federico Faggin and Ralph Ungermann at the end of 1974.[34][35]

Description

The 4004 employs an 10 μm process silicon-gate enhancement-load pMOS technology on a 12 mm2 die[37] and can execute approximately 92000 instructions per second; a single instruction cycle is 10.8 microseconds.[38] The original clock rate design goal was 1 MHz, the same as the IBM 1620 Model I.

The Intel 4004 was fabricated using masks produced by physically cutting each pattern at 500x magnification on a large sheet of Rubylith photo-reducing it, and repeating, a process made obsolete by current computer graphic design capabilities.[39]

For the purpose of testing the produced chips, Faggin developed a tester for silicon wafers of MCS-4 family that was itself driven by 4004 chip. The tester also served as a proof for the management that Intel 4004 microprocessor could be used not only in calculator-like products, but also for control applications.[40]

The 4004 includes functions for direct low-level control of memory-chip selection and I/O, which are not normally handled by the microprocessor; however, its functionality is limited in that it cannot execute code from RAM and is limited to whatever instructions are provided in ROM (or an independently loaded RAM working as ROM—in either case, the processor is itself unable to write or transfer data into an executable memory space). The RAM and ROM parts chips also unusual in their integration of I/O functions together with their primary memory function. this partitioning significantly reduced the minimum part count in an MCS-4 system, but required inclusion of a certain amount of processor-like logic on the memory chips themselves to accept, decode and execute relatively high-level data-transfer instructions.

The standard arrangement for a 4004 system is anything up to 16 × 4001 ROM chips (in a single bank) and 16 × 4002 RAM chips (in four banks of four), which together provide the 4 KB program storage, 1024 + 256 nibbles of data/status storage, plus 64 output and 64 input/output external data/control lines (which can themselves be used to operate, e.g. a 4003). Intel's MCS-4 documentation, however, claims that up to 48 ROM and RAM chips (providing up to 192 external control lines) "in any combination" can be connected to the 4004 "with simple gating hardware", but declines to give any further detail or examples of how this would actually be achieved.

Technical specifications

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

- Maximum clock rate is 740 kHz. The 4004 had this maximum clock rating upon its initial 1971 release.[lower-alpha 2]

- Instruction cycle time: minimum 10.8 μs[38] (8 clock cycles per machine cycle).

- Instruction execution time 1 or 2 machine cycles (10.8 or 21.6 μs), 46250 to 92500 instructions per second.

- Adding two 8-digit decimal numbers (32 bits each, assuming 4-bit BCD digits) takes a claimed 850 μs, or approximately 79 machine cycles (632 clock ticks), for an average of just under 10 cycles (80 ticks) per digit pair and an operating speed of 1176 × 8-digit additions per second[lower-alpha 3]

- Separate program and data storage. Contrary to Harvard architecture designs, however, which use separate buses, the 4004, with its need to keep pin count down, uses a single multiplexed 4-bit bus for transferring:

- 12-bit addresses,

- 8-bit instructions,

- 4-bit data words.

- Able to directly address 5120 bits (equivalent to 640 bytes) of RAM, stored as 1280 4-bit "characters" and organized into groups representing 1024 "data" and 256 "status" characters (512 and 128 bytes).[lower-alpha 4]

- Able to directly address 32768 bits of ROM, equivalent to and arranged as 4096 8-bit words (i.e. bytes).[lower-alpha 5]

- Instruction set contained 46 instructions (of which 41 were 8 bits wide and 5 were 16 bits wide).

- Register set contains 16 registers of 4 bits each.

- Internal subroutine stack, 3 levels deep.

Logic levels

| Symbol | Min. | Max |

|---|---|---|

| VSS–DD | +15 V − 5% | +15 V + 5% |

| VIL | VDD | VSS − 5.5 V |

| VIH | VSS − 1.5 V | VSS + 0.3 V |

| VOL | VSS − 12 V | VSS − 6.5 V |

| VOH | VSS − 0.5 V | VSS |

Support chips

- 4001: 256-byte ROM (256 8-bit program instructions) and one built-in 4-bit I/O port. A 4001 ROM+I/O chip cannot be used in a system along with a 4008/4009 pair.[41]

- 4002: 40-byte RAM (80 4-bit data words) and one built-in 4-bit output port; the RAM portion of the chip is organized into 4 "registers" of 20 4-bit words:

- 4003: 10-bit parallel output shift register for scanning keyboards, displays, printers, etc.

- 4008: 8-bit address latch for access to standard memory chips and one built-in 4-bit chip-select and I/O port.

- 4009: program and I/O access converter to standard memory and I/O chips.

- 4269: keyboard/display interface.

- 4289: memory interface (combined functions of 4008 and 4009).

The minimum system specification described by Intel consists of a 4004 with a single 256-byte 4001 program ROM; there is no explicit need for separate RAM in minimal-complexity applications thanks to the 4004's large number of onboard index registers, which represent the equivalent of 16 × 4-bit or 8 × 8-bit characters (or a mixture) of working RAM, nor for simple interface chips thanks to the ROM's built-in I/O lines. However, as project complexity increases, the various other support chips start to become useful.

Packaging

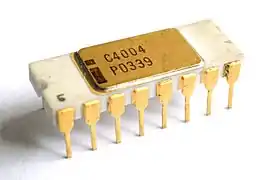

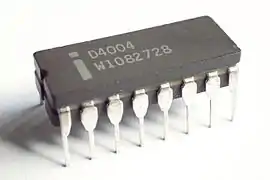

Numerous versions of the Intel MCS-4 line of processors were produced. The earliest versions, marked C (like C4004), were ceramic and used a zebra pattern of white and gray on the back of the chips, often called "grey traces". The next generation of the chips was plain white ceramic (also marked C), and then dark gray ceramic (D). Many of the more recent versions of MCS-4 family were also produced with plastic (P).

The ceramic C4004 variant without gray traces

The ceramic C4004 variant without gray traces The ceramic D4004 variant

The ceramic D4004 variant The plastic P4004 variant

The plastic P4004 variant

Use

The first commercial product to use a microprocessor was the Busicom calculator 141-PF. The 4004 was also used in the first microprocessor-controlled pinball game, a prototype produced by Dave Nutting Associates for Bally in 1974.

In 1996, The US Patent Office officially recognized Mr. Gary W. Boone and his employer, Texas Instruments, as the inventors of the single-chip microcontroller, overturning the patent grant to Gilbert P. Hyatt in 1990. Even though the patent had expired, it was thought to have potential financial impact depending on the details of previous contracts with Gilbert Hyatt.[42] According to Nick Tredennick, a microprocessor designer and expert witness to that Boone/Hyatt patent case:

Here are my opinions from [the] study [I conducted for the patent case]. The first microprocessor in a commercial product was the Four Phase Systems AL1. The first commercially available (sold as a component) microprocessor was the 4004 from Intel.[43]

A popular myth has it that Pioneer 10, the first spacecraft to leave the solar system, used an Intel 4004 microprocessor. According to Dr. Larry Lasher of Ames Research Center, the Pioneer team did evaluate the 4004, but decided it was too new at the time to include in any of the Pioneer projects. The myth was repeated by Federico Faggin himself in a lecture for the Computer History Museum in 2006.[44]

Legacy and value

Federico Faggin signed the 4004 with his initials because he knew that his silicon gate design embodied "the essence of the microprocessor". A corner of the die reads "F.F."[25]

On November 15, 2006, the 35th anniversary of the 4004, Intel celebrated by releasing the chip's schematics, mask works, and user manual.[45] A fully functional 41 × 58 cm,[46] 130× scale replica of the Intel 4004 was built using discrete transistors and put on display in 2006 at the Intel Museum in Santa Clara, California.[47]

On October 15, 2010, Faggin, Hoff, and Mazor were awarded the National Medal of Technology and Innovation by President Barack Obama for their pioneering work on the 4004.[48]

See also

Notes

- ↑ Several microprocessors had been designed or built by this point, but were not available for purchase outside the products they were part of.

- ↑ Although the early documentation states "0.75 MHz", this is at odds with the timing diagrams, which specify a minimum overall cycle time of 1350 ns (=741 kHz) and a maximum of 2010 ns (=498 kHz).

- ↑ This statistic comes from the same document as the "0.75 MHz" claim and which appears to inaccurately round off the true figures for the purposes of summary. 850 μs with a minimum 10.8 μs cycle time would in truth be 78.7 machine cycles, or roughly 629 clock ticks. As the processor is locked into an 8-tick cycle, it is more likely that this operation would take 79 or even 80 full cycles, thus 632 to 640 ticks and 853 to 864 μs (or 854 to 865 μs at a true 740 kHz), and reducing the actual execution speed to 1157–1172 (or 1156–1171) 8-digit additions per second.

- ↑ However, this could only be used as working / data memory, and was non-executable: program code could not be stored in or run from RAM, as the processor kept the two memory areas strictly segregated at the microcode level. Instruction fetching forced assertion of the ROM chip-select line (and deassertion of the RAM select lines), and the chip had no way to "write" data to anything other than an IO port whilst the ROM area was selected.

- ↑ The only part of the 4004 memory space capable of storing executable code, though also usable for general-purpose storage.

References

- ↑ "The Life Cycle of a CPU". www.cpushack.com.

- ↑ "The 40th birthday of—maybe—the first microprocessor, the Intel 4004". 2011-11-15.

- ↑ "Inflation Calculator | Find US Dollar's Value From 1913-2023". www.usinflationcalculator.com. 2023-05-10. Retrieved 2023-05-25.

- ↑ "The Story of the Intel 4004". Intel.

- ↑ "The Intel 4004 Microprocessor and the Silicon Gate Technology: The Busicom Engineering Prototype". Intel4004.com.

- ↑ "Olivetti Programma 101 Electronic Calculator". The Old Calculator Web Museum.

technically, the machine was a programmable calculator, not a computer.

- ↑ "2008/107/1 Computer, Programma 101, and documents (3), plastic / metal / paper / electronic components, hardware architect Pier Giorgio Perotto, designed by Mario Bellini, made by Olivetti, Italy, 1965–1971". www.powerhousemuseum.com. Retrieved 2016-03-20.

- ↑ Faggin et al. 1996, p. 10.

- 1 2 3 Faggin et al. 1996, p. 11.

- 1 2 3 Faggin et al. 1996, p. 12.

- ↑ Possibly he had confused the Plessey name with that of Massey Ferguson, makers of agricultural machinery.

- ↑ Aspray, William (1994-05-25). "Oral-History: Tadashi Sasaki". Interview #211 for the Center for the History of Electrical Engineering. The Institute of Electrical and Electronics Engineers, Inc. Retrieved 2013-01-02.

- ↑ Faggin et al. 1996, p. 13.

- ↑ Faggin et al. 1996, p. 14.

- 1 2 3 Faggin et al. 1996, p. 15.

- 1 2 3 4 Faggin et al. 1996, p. 16.

- ↑ Faggin, Federico. "A faster generation of MOS devices with low thresholds is riding the crest of the new wave, silicon-gate IC's". Retrieved 2017-06-03.

- ↑ Faggin, Federico. "Earliest Published Papers". Retrieved 2017-06-03.

- ↑ Faggin, Federico. "The New Methodology for Random Logic Design". Retrieved 2017-06-03.

- ↑ Federico Faggin, T. Klein (1970). "Silicon-Gate Technology". Solid State Electronics. Vol. 13. pp. 1125–1144

- ↑ Cass, Stephan (2021). "Intel's 4004 Turns 50". IEEE Spectrum. 58 (11): 9–10.

- ↑ Faggin, Federico. "The Buried Contact". Retrieved 2017-06-03.

- ↑ "Inductee Detail". National Inventors Hall of Fame. July 25, 2016.

- ↑ Faggin, Federico. "The Bootstrap Load". Retrieved 2017-06-03.

- 1 2 3 "Federico Faggin's Signature". Intel4004.com. Retrieved 2012-08-21.

- 1 2 3 Faggin et al. 1996, p. 17.

- ↑ "Intel 4004 Microprocessor 35th Anniversary". YouTube.

- 1 2 3 Faggin et al. 1996, p. 18.

- ↑ Cass, Stephen (2018-07-02). "Chip Hall of Fame: Intel 4004 Microprocessor". Retrieved 2019-02-05.

- ↑ Gilder, George (1990). Microcosm: the quantum revolution in economics and technology. Simon and Schuster. p. 107. ISBN 978-0-671-70592-3.

Intel's first advertisement for the 4004 appeared in the November 15, 1971 issue of Electronic News

- 1 2 3 Faggin et al. 1996, p. 19.

- ↑ Woerner, Joerg (2001-11-16). "The "Calculator-on-a-chip"". Datamath Calculator Museum. Retrieved 2016-03-22.

- ↑ Woerner, Joerg (2001-02-26). "Texas Instruments: They invented the Microcontroller". Datamath Calculator Museum. Retrieved 2016-03-22.

- ↑ "ZILOG Oral History Panel on the Founding of the Company and the development of the Z80 Microprocessor" (PDF).

- ↑ "Zilog | History of Computer Communications". historyofcomputercommunications.info.

- ↑ Intel 4004 microprocessor family, retrieved December 14, 2011.

- ↑ "History of Computing Industrial Era 1970–1971". 2010-10-19. Archived from the original on 2012-06-25. Retrieved 2016-05-05.

In February Intel releases the 4004 microprocessor to the market. It has 12 sq mm die size and 16 pins which fit into a motherboard.

- 1 2 "Intel 4004 datasheet" (PDF) (published 2010-07-06). 1987. Archived from the original (PDF) on 2011-06-01. Retrieved 2020-12-18.

- ↑ "Intel's Accidental Revolution". CNet.com. Archived from the original on 2012-07-11. Retrieved 2009-07-30.

- ↑ Hendrie, Gardner (2006). "Oral History of Federico Faggin" (PDF). Computer History Museum. Archived from the original (PDF) on 2017-01-10. Retrieved 2017-01-24.

- ↑ IMPORTANT section at page 25: http://www.intel.com/Assets/PDF/Manual/msc4.pdf.

- ↑ John Markoff (1996-06-20). "For Texas Instruments, Some Bragging Rights". New York Times.

- ↑ "Dissertation 2004" (PDF). Archived (PDF) from the original on 2011-08-14. Retrieved 2017-11-14.

- ↑ "Intel 4004 Microprocessor 35th Anniversary". YouTube. Retrieved 2011-07-06.

- ↑ Intel 4004 Microprocessor Historical Materials, Intel Museum, 2009-11-15, accessed November 18, 2009

- ↑ "4004 @ 44: SVG Mask Artwork; New Busicom 141-PF replica PCB; Printer emulator". 2015-11-20. Retrieved 2016-05-05.

- ↑ "Intel 4004 -- 45th Anniversary Project". 2015-11-15. Retrieved 2016-04-02.

including fully functional 130x scale replicas of the 4004 built using discrete transistors, museum-durable keyboards and slide switches, and video display electronics.

- ↑ "President Obama Honors Nation's Top Scientists and Innovators". whitehouse.gov (Press release). 2010-10-15 – via National Archives.

Sources

Bibliography

- Faggin, Federico; Hoff, Marcian Jr.; Mazor, Stanley; Shima, Masatoshi (December 1996). "The History of the 4004". IEEE Micro. 16 (6): 10–20. doi:10.1109/40.546561.

- Federico Faggin: The MOS silicon gate technology and the first microprocessors published in La Rivista del Nuovo Cimento by Italian Physical Society and European Physical Society, October 8, 2015, Vol .38, N.12 (pp 575-619)

- Federico Faggin: SILICON: From the invention of the microprocessor to the new science of consciousness. Autobiography from the leader and key developer of the silicon gate technology and the first microprocessors projects, founder of Zilog and developer of the Z80 CPU. by Waterside Productions in 2020.

Patents

- US 3753011 August 14, 1973. Faggin, Federico: Power supply settable bi-stable circuit.

- US 3821715 June 28, 1974. Hoff, Marcian; Mazor, Stanley; Faggin, Federico: Memory system for multi-chip digital computer.

Historical documents

Earliest documents on the MOS silicon gate technology for integrated circuits that enabled the 4004

- Faggin, F., Klein, T., and Vadasz, L.: Insulated Gate Field Effect Transistor Integrated Circuits with Silicon Gates.Cover and abstract of the IEDM (International Electron Devices Meeting) Program (October 1968). The Silicon Gate Technology (SGT), created at Fairchild Semiconductor in 1968, was first presented by its co-inventor and developer, Federico Faggin, at the IEDM on October 23, 1968, in Washington, D.C. It was the only commercial process technology for the fabrication of MOS integrated circuits with self-aligned gate that was later universally adopted by the semiconductor industry. The SGT was the first technology to produce commercial dynamic RAMs, CCD image sensors, non volatile memories and the microprocessor, providing for the first time all the fundamental elements of a general purpose computer with LSI integrated circuits.

- Federico Faggin and Thomas Klein.: "A Faster Generation of MOS Devices with Low Thresholds is Riding the Crest of the New Wave, Silicon-Gate IC's".Cover of Electronics Magazine (29 September 1969). The Electronics article introduces the Fairchild 3708, designed by Federico Faggin in 1968. It was the world's first commercial integrated circuit using the Silicon Gate Technology, proving its viability, and it was the first application of the new technology.

- F. Faggin, T. Klein: Silicon-Gate Technology. "Solid State Electronics", 1970, Vo. 13, pp. 1125–1144

Earliest documents on the Intel 4004

- Initials F.F. (Federico Faggin) on the 4004 design (1971). The 4004 bears the initials F.F. of its designer, Federico Faggin, etched on one corner of the chip. Signing the chip was a spontaneous gesture of proud authorship and was also an original idea imitated after him by many Intel designers.

- F. Faggin and M. E. Hoff: "Standard parts and custom design merge in four-chip processor kit". Electronics/April 24, 1972, pp. 112–116. Reprinted on pp. 6–27 to 6–31 of The Intel Memory Design Handbook: August 1973.

- F. Faggin, M. Shima, M. E. Hoff Jr., H. Feeney, S. Mazor: "The MCS-4—An LSI micro computer system". IEEE '72 Region Six Conference. Reprinted on pp. 6–32 to 6–37 of The Intel Memory Design Handbook: August 1973.

- Busicom 141-PF Printing Calculator Engineering Prototype (1971). (Gift of Federico Faggin to the Computer History Museum, Mountain View, CA). The CHM collection catalog shows pictures of the engineering prototype of the Busicom 141-PF desktop calculator. The engineering prototype used the world's first microprocessor to have ever been produced. This one-of-a-kind prototype was a personal present by Busicom's president Mr. Yoshio Kojima to Federico Faggin for his successful leadership of the design and development of the 4004 and three other memory and I/O chips (the MCS-4 chipset). After keeping it in his home for 25 years, Faggin donated it to the CHM in 1996.

- Faggin, F.; Capocaccia, F. "A New Integrated MOS Shift Register", Proceedings XV International Electronics Scientific Congress, Rome, April 1968, pp. 143–152. This paper describes a novel static MOS shift register, developed at SGS-Fairchild (now ST Micro) at the end of 1967, before Federico Faggin joined Fairchild's R&D in Palo Alto (Ca) in February 1968. Faggin later used this new shift register in the MCS-4 chips, including the 4004(1970).

Further reading

- Intel 4004 Microprocessor 35th Anniversary - Live recording of presentations by Ted Hoff and Federico Faggin at the Computer History Museum for the 35th anniversary of the first microprocessor. (youtube.com)

- IEEE Solid State Circuits Magazine, Winter 2009 Vol.1 No.1. "The 4004 microprocessor of Faggin, Hoff, Mazor, and Shima".

- The MOS Silicon Gate Technology and the First Microprocessors, by Federico Faggin published in La Rivista del Nuovo Cimento, Italian Physical Society, Vol. 38, No. 12, 2015.

- "How we made the microprocessor" by Federico Faggin. Nature Electronics, Vol. 1, January 2018. Published online: 2018-01-08

External links

- Intel's First Microprocessor—the Intel 4004: Intel Museum (Intel Corporate Archives) entry

- The Intel 4004: A testimonial from Federico Faggin, designer of the 4004 and developer of its enabling technology

- The New Methodology for Random Logic Design Used in the 4004 and in All the Early Intel Microprocessors

- Interview with Masatoshi Shima

- MCS-4 Micro Computer Set Data Sheet (12 pp)

- Intel 4004 -- 45th Anniversary Project, Schematics at the unofficial 4004 website, and a simulator in Java. Fully functional 130x scale replicas of the 4004 built using discrete transistors.

- The Crucial Role of Silicon Design in the Invention of the Microprocessor

- High resolution light microscope pictures of an Intel 4004 die together with a basic explanation of CMOS logic

- Intel 4004 Emulator, Assembler, and Disassembler: Simple programming tools for Intel 4004 in Javascript

- Datasheet Intel 4004

- Datasheet Intel MCS-4

- BuscomV2p1 schematic

- MSC-4 Assembly Language Programming Manual

- Chip Hall of Fame: Intel 4004 Microprocessor (IEEE Spectrum website)

- Story of the Intel 4004