Video Code Engine (VCE, was earlier referred to as Video Coding Engine,[1] Video Compression Engine[2] or Video Codec Engine[3] in official AMD documentation) is AMD's video encoding application-specific integrated circuit implementing the video codec H.264/MPEG-4 AVC. Since 2012 it was integrated into all of their GPUs and APUs except Oland.

VCE was introduced with the Radeon HD 7000 Series on 22 December 2011.[4][5][6] VCE occupies a considerable amount of the die surface at the time of its introduction[7] and is not to be confused with AMD's Unified Video Decoder (UVD).

As of AMD Raven Ridge (released January 2018), UVD and VCE were succeeded by Video Core Next (VCN).

Overview

The handling of video data involves computation of data compression algorithms and possibly of video processing algorithms. As the template compression methods shows, lossy video compression algorithms involve the steps: motion estimation (ME), discrete cosine transform (DCT), and entropy encoding (EC).

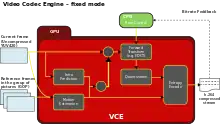

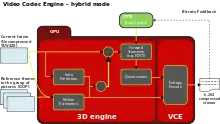

AMD Video Code Engine (VCE) is a full hardware implementation of the video codec H.264/MPEG-4 AVC. It is capable of delivering 1080p at 60 frames/sec. Because its entropy encoding block is also a separately accessible Video Codec Engine, it can be operated in two modes: full-fixed mode and hybrid mode.[8][9]

By employing AMD APP SDK, available for Linux and Microsoft Windows, developers can create hybrid encoders that pair custom motion estimation, inverse discrete cosine transform and motion compensation with the hardware entropy encoding to achieve faster than real-time encoding. In hybrid mode, only the entropy encoding block of the VCE unit is used, while the remaining computation is offloaded to the 3D engine of the GPU, so the computing scales with the number of available compute units (CUs).

VCE 1.0

As of April 2014, there are two versions of VCE.[1] Version 1.0 supports H.264 YUV420 (I & P frames), H.264 SVC Temporal Encode VCE, and Display Encode Mode (DEM).

It can be found on:

- Piledriver-based

- Trinity APUs (Ax-5xxx, e.g. A10-5800K)

- Richland APUs (Ax-6xxx, e.g. A10-6800K)

- GPUs of the Southern Islands generation (GCN1: CAYMAN, ARUBA (Trinity/Richland), CAPE VERDE, PITCAIRN, TAHITI). These are

- Radeon HD 7700 series (except HD 7790 with VCE 2.0)

- Radeon HD 7800 series

- Radeon HD 7900 series

- Radeon HD 8570 to 8990 (except HD 8770 with VCE 2.0)

- Radeon R7 250E, 250X, 265 / R9 270, 270X, 280, 280X

- Radeon R7 360, 370, 455 / R9 370, 370X

- Mobile Radeon HD 77x0M to HD 7970M

- Mobile Radeon HD 8000-Series

- Mobile Radeon Rx M2xx Series (except R9 M280X with VCE 2.0 and R9 M295X with VCE 3.0)

- Mobile Radeon R5 M330 to R9 M390

- FirePro cards with 1st Generation GCN (GCN1) (Except W2100, which is Oland XT)

VCE 2.0

Compared to the first version, VCE 2.0 adds H.264 YUV444 (I-Frames), B-frames for H.264 YUV420, and improvements to the DEM (Display Encode Mode), which results in a better encoding quality.

It can be found on:

- Steamroller-based

- Kaveri APUs (Ax-7xxx, e.g. A10-7850K)

- Godavari APUs (Ax-7xxx, e.g. A10-7890K)

- Jaguar-based

- Kabini APUs (e.g. Athlon 5350, Sempron 2650)

- Temash APUs (e.g. A6-1450, A4-1200)

- Puma-based

- Beema and Mullins

- GPUs of the Sea Islands generation as well Bonaire or Hawaii GPUs (2nd Generation Graphics Core Next), such as

- Radeon HD 7790, 8770

- Radeon R7 260, 260X / R9 290, 290X, 295X2

- Radeon R7 360 / R9 390, 390X

- Mobile Radeon R9 M280X

- Mobile Radeon R9 M385, M385X

- Mobile Radeon R9 M470, M470X

- FirePro cards with 2nd Generation GCN (GCN2)

VCE 3.0

Video Code Engine 3.0 (VCE 3.0) technology features a new high-quality video scaling and - since version 3.4 - High Efficiency Video Coding (HEVC/H.265).[10][11]

It, together with UVD 6.0, can be found on 3rd generation of Graphics Core Next (GCN3) with "Tonga", "Fiji", "Iceland", and "Carrizo" (VCE 3.1) based graphics controller hardware, which is now used AMD Radeon Rx 300 Series (Pirate Islands GPU family) and VCE 3.4 by actual AMD Radeon Rx 400 Series and AMD Radeon 500 Series (both Polaris GPU family).

- Tonga: Radeon R9 285, 380, 380X; Mobile Radeon R9 M390X, M395, M395X, M485X

- Tonga XT: FirePro W7100, S7100X, S7150, S7150 X2

- Fiji: Radeon R9 Fury, Fury X, Nano; Radeon Pro Duo (2016); FirePro S9300, W7170M ; Instinct MI8

- Polaris: RX 460, 470, 480; RX 550, 560, 570, 580; Radeon Pro Duo (2017)

VCE 3.0 removes support for H.264 B-frames.[12]

VCE 4.0

The Video Code Engine 4.0 encoder and UVD 7.0 decoder are included in the Vega-based GPUs.[13][14]

VCE 4.1

AMD's Vega20 GPU, present in the Instinct Mi50, Instinct Mi60 and Radeon VII cards, include VCE 4.1 and two UVD 7.2 instances.[15][16]

Feature overview

APUs

The following table shows features of AMD's processors with 3D graphics, including APUs (see also: List of AMD processors with 3D graphics).

| Platform | High, standard and low power | Low and ultra-low power | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Codename | Server | Basic | Toronto | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Micro | Kyoto | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Desktop | Performance | Raphael | Phoenix | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Mainstream | Llano | Trinity | Richland | Kaveri | Kaveri Refresh (Godavari) | Carrizo | Bristol Ridge | Raven Ridge | Picasso | Renoir | Cezanne | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Entry | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Basic | Kabini | Dalí | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Mobile | Performance | Renoir | Cezanne | Rembrandt | Dragon Range | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Mainstream | Llano | Trinity | Richland | Kaveri | Carrizo | Bristol Ridge | Raven Ridge | Picasso | Renoir Lucienne |

Cezanne Barceló |

Phoenix | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Entry | Dalí | Mendocino | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Basic | Desna, Ontario, Zacate | Kabini, Temash | Beema, Mullins | Carrizo-L | Stoney Ridge | Pollock | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Embedded | Trinity | Bald Eagle | Merlin Falcon, Brown Falcon |

Great Horned Owl | Grey Hawk | Ontario, Zacate | Kabini | Steppe Eagle, Crowned Eagle, LX-Family |

Prairie Falcon | Banded Kestrel | River Hawk | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Released | Aug 2011 | Oct 2012 | Jun 2013 | Jan 2014 | 2015 | Jun 2015 | Jun 2016 | Oct 2017 | Jan 2019 | Mar 2020 | Jan 2021 | Jan 2022 | Sep 2022 | Jan 2023 | Jan 2011 | May 2013 | Apr 2014 | May 2015 | Feb 2016 | Apr 2019 | Jul 2020 | Jun 2022 | Nov 2022 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| CPU microarchitecture | K10 | Piledriver | Steamroller | Excavator | "Excavator+"[17] | Zen | Zen+ | Zen 2 | Zen 3 | Zen 3+ | Zen 4 | Bobcat | Jaguar | Puma | Puma+[18] | "Excavator+" | Zen | Zen+ | "Zen 2+" | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| ISA | x86-64 v1 | x86-64 v2 | x86-64 v3 | x86-64 v4 | x86-64 v1 | x86-64 v2 | x86-64 v3 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Socket | Desktop | Performance | — | AM5 | — | — | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Mainstream | — | AM4 | — | — | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Entry | FM1 | FM2 | FM2+ | FM2+[lower-alpha 1], AM4 | AM4 | — | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Basic | — | — | AM1 | — | FP5 | — | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Other | FS1 | FS1+, FP2 | FP3 | FP4 | FP5 | FP6 | FP7 | FL1 | FP7 FP7r2 FP8 |

? | FT1 | FT3 | FT3b | FP4 | FP5 | FT5 | FP5 | FT6 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| PCI Express version | 2.0 | 3.0 | 4.0 | 5.0 | 4.0 | 2.0 | 3.0 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| CXL | — | — | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Fab. (nm) | GF 32SHP (HKMG SOI) |

GF 28SHP (HKMG bulk) |

GF 14LPP (FinFET bulk) |

GF 12LP (FinFET bulk) |

TSMC N7 (FinFET bulk) |

TSMC N6 (FinFET bulk) |

CCD: TSMC N5 (FinFET bulk) cIOD: TSMC N6 (FinFET bulk) |

TSMC 4nm (FinFET bulk) |

TSMC N40 (bulk) |

TSMC N28 (HKMG bulk) |

GF 28SHP (HKMG bulk) |

GF 14LPP (FinFET bulk) |

GF 12LP (FinFET bulk) |

TSMC N6 (FinFET bulk) | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Die area (mm2) | 228 | 246 | 245 | 245 | 250 | 210[19] | 156 | 180 | 210 | CCD: (2x) 70 cIOD: 122 |

178 | 75 (+ 28 FCH) | 107 | ? | 125 | 149 | ~100 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Min TDP (W) | 35 | 17 | 12 | 10 | 15 | 105 | 35 | 4.5 | 4 | 3.95 | 10 | 6 | 12 | 8 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max APU TDP (W) | 100 | 95 | 65 | 45 | 170 | 54 | 18 | 25 | 6 | 54 | 15 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max stock APU base clock (GHz) | 3 | 3.8 | 4.1 | 4.1 | 3.7 | 3.8 | 3.6 | 3.7 | 3.8 | 4.0 | 3.3 | 4.7 | 4.3 | 1.75 | 2.2 | 2 | 2.2 | 3.2 | 2.6 | 1.2 | 3.35 | 2.8 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max APUs per node[lower-alpha 2] | 1 | 1 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max core dies per CPU | 1 | 2 | 1 | 1 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max CCX per core die | 1 | 2 | 1 | 1 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max cores per CCX | 4 | 8 | 2 | 4 | 2 | 4 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max CPU[lower-alpha 3] cores per APU | 4 | 8 | 16 | 8 | 2 | 4 | 2 | 4 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max threads per CPU core | 1 | 2 | 1 | 2 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Integer pipeline structure | 3+3 | 2+2 | 4+2 | 4+2+1 | 1+3+3+1+2 | 1+1+1+1 | 2+2 | 4+2 | 4+2+1 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| i386, i486, i586, CMOV, NOPL, i686, PAE, NX bit, CMPXCHG16B, AMD-V, RVI, ABM, and 64-bit LAHF/SAHF | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| IOMMU[lower-alpha 4] | — | v2 | v1 | v2 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| BMI1, AES-NI, CLMUL, and F16C | — | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| MOVBE | — | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| AVIC, BMI2, RDRAND, and MWAITX/MONITORX | — | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| SME[lower-alpha 5], TSME[lower-alpha 5], ADX, SHA, RDSEED, SMAP, SMEP, XSAVEC, XSAVES, XRSTORS, CLFLUSHOPT, CLZERO, and PTE Coalescing | — | — | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| GMET, WBNOINVD, CLWB, QOS, PQE-BW, RDPID, RDPRU, and MCOMMIT | — | — | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| MPK, VAES | — | — | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| SGX | — | — | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| FPUs per core | 1 | 0.5 | 1 | 1 | 0.5 | 1 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Pipes per FPU | 2 | 2 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| FPU pipe width | 128-bit | 256-bit | 80-bit | 128-bit | 256-bit | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| CPU instruction set SIMD level | SSE4a[lower-alpha 6] | AVX | AVX2 | AVX-512 | SSSE3 | AVX | AVX2 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 3DNow! | 3DNow!+ | — | — | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| PREFETCH/PREFETCHW | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| GFNI | — | — | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| AMX | — | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| FMA4, LWP, TBM, and XOP | — | — | — | — | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| FMA3 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| AMD XDNA | — | — | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| L1 data cache per core (KiB) | 64 | 16 | 32 | 32 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| L1 data cache associativity (ways) | 2 | 4 | 8 | 8 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| L1 instruction caches per core | 1 | 0.5 | 1 | 1 | 0.5 | 1 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max APU total L1 instruction cache (KiB) | 256 | 128 | 192 | 256 | 512 | 256 | 64 | 128 | 96 | 128 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| L1 instruction cache associativity (ways) | 2 | 3 | 4 | 8 | 2 | 3 | 4 | 8 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| L2 caches per core | 1 | 0.5 | 1 | 1 | 0.5 | 1 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max APU total L2 cache (MiB) | 4 | 2 | 4 | 16 | 1 | 2 | 1 | 2 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| L2 cache associativity (ways) | 16 | 8 | 16 | 8 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max on--die L3 cache per CCX (MiB) | — | 4 | 16 | 32 | — | 4 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max 3D V-Cache per CCD (MiB) | — | 64 | — | — | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max total in-CCD L3 cache per APU (MiB) | 4 | 8 | 16 | 64 | 4 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max. total 3D V-Cache per APU (MiB) | — | 64 | — | — | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max. board L3 cache per APU (MiB) | — | — | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max total L3 cache per APU (MiB) | 4 | 8 | 16 | 128 | 4 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| APU L3 cache associativity (ways) | 16 | 16 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| L3 cache scheme | Victim | Victim | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max. L4 cache | — | — | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max stock DRAM support | DDR3-1866 | DDR3-2133 | DDR3-2133, DDR4-2400 | DDR4-2400 | DDR4-2933 | DDR4-3200, LPDDR4-4266 | DDR5-4800, LPDDR5-6400 | DDR5-5200 | DDR5-5600, LPDDR5x-7500 | DDR3L-1333 | DDR3L-1600 | DDR3L-1866 | DDR3-1866, DDR4-2400 | DDR4-2400 | DDR4-1600 | DDR4-3200 | LPDDR5-5500 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max DRAM channels per APU | 2 | 1 | 2 | 1 | 2 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max stock DRAM bandwidth (GB/s) per APU | 29.866 | 34.132 | 38.400 | 46.932 | 68.256 | 102.400 | 83.200 | 120.000 | 10.666 | 12.800 | 14.933 | 19.200 | 38.400 | 12.800 | 51.200 | 88.000 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| GPU microarchitecture | TeraScale 2 (VLIW5) | TeraScale 3 (VLIW4) | GCN 2nd gen | GCN 3rd gen | GCN 5th gen[20] | RDNA 2 | RDNA 3 | TeraScale 2 (VLIW5) | GCN 2nd gen | GCN 3rd gen[20] | GCN 5th gen | RDNA 2 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| GPU instruction set | TeraScale instruction set | GCN instruction set | RDNA instruction set | TeraScale instruction set | GCN instruction set | RDNA instruction set | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max stock GPU base clock (MHz) | 600 | 800 | 844 | 866 | 1108 | 1250 | 1400 | 2100 | 2400 | 400 | 538 | 600 | ? | 847 | 900 | 1200 | 600 | 1300 | 1900 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Max stock GPU base GFLOPS[lower-alpha 7] | 480 | 614.4 | 648.1 | 886.7 | 1134.5 | 1760 | 1971.2 | 2150.4 | 3686.4 | 102.4 | 86 | ? | ? | ? | 345.6 | 460.8 | 230.4 | 1331.2 | 486.4 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| 3D engine[lower-alpha 8] | Up to 400:20:8 | Up to 384:24:6 | Up to 512:32:8 | Up to 704:44:16[21] | Up to 512:32:8 | 768:48:8 | 128:8:4 | 80:8:4 | 128:8:4 | Up to 192:12:8 | Up to 192:12:4 | 192:12:4 | Up to 512:?:? | 128:?:? | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| IOMMUv1 | IOMMUv2 | IOMMUv1 | ? | IOMMUv2 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Video decoder | UVD 3.0 | UVD 4.2 | UVD 6.0 | VCN 1.0[22] | VCN 2.1[23] | VCN 2.2[23] | VCN 3.1 | ? | UVD 3.0 | UVD 4.0 | UVD 4.2 | UVD 6.0 | UVD 6.3 | VCN 1.0 | VCN 3.1 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Video encoder | — | VCE 1.0 | VCE 2.0 | VCE 3.1 | — | VCE 2.0 | VCE 3.1 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| AMD Fluid Motion | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| GPU power saving | PowerPlay | PowerTune | PowerPlay | PowerTune[24] | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| TrueAudio | — | ? | — | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| FreeSync | 1 2 |

1 2 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| HDCP[lower-alpha 9] | ? | 1.4 | 2.2 | 2.3 | ? | 1.4 | 2.2 | 2.3 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| PlayReady[lower-alpha 9] | — | 3.0 not yet | — | 3.0 not yet | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Supported displays[lower-alpha 10] | 2–3 | 2–4 | 3 | 3 (desktop) 4 (mobile, embedded) | 4 | 2 | 3 | 4 | 4 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

/drm/radeon[lower-alpha 11][27][28] | — | — | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

/drm/amdgpu[lower-alpha 11][29] | — | — | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

- ↑ For FM2+ Excavator models: A8-7680, A6-7480 & Athlon X4 845.

- ↑ A PC would be one node.

- ↑ An APU combines a CPU and a GPU. Both have cores.

- ↑ Requires firmware support.

- 1 2 Requires firmware support.

- ↑ No SSE4. No SSSE3.

- ↑ Single-precision performance is calculated from the base (or boost) core clock speed based on a FMA operation.

- ↑ Unified shaders : texture mapping units : render output units

- 1 2 To play protected video content, it also requires card, operating system, driver, and application support. A compatible HDCP display is also needed for this. HDCP is mandatory for the output of certain audio formats, placing additional constraints on the multimedia setup.

- ↑ To feed more than two displays, the additional panels must have native DisplayPort support.[26] Alternatively active DisplayPort-to-DVI/HDMI/VGA adapters can be employed.

- 1 2 DRM (Direct Rendering Manager) is a component of the Linux kernel. Support in this table refers to the most current version.

GPUs

The following table shows features of AMD/ATI's GPUs (see also: List of AMD graphics processing units).

| Name of GPU series | Wonder | Mach | 3D Rage | Rage Pro | Rage 128 | R100 | R200 | R300 | R400 | R500 | R600 | RV670 | R700 | Evergreen | Northern Islands |

Southern Islands |

Sea Islands |

Volcanic Islands |

Arctic Islands/Polaris |

Vega | Navi 1x | Navi 2x | Navi 3x | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Released | 1986 | 1991 | Apr 1996 |

Mar 1997 |

Aug 1998 |

Apr 2000 |

Aug 2001 |

Sep 2002 |

May 2004 |

Oct 2005 |

May 2007 |

Nov 2007 |

Jun 2008 |

Sep 2009 |

Oct 2010 |

Jan 2012 |

Sep 2013 |

Jun 2015 |

Jun 2016, Apr 2017, Aug 2019 | Jun 2017, Feb 2019 | Jul 2019 |

Nov 2020 |

Dec 2022 | |||

| Marketing Name | Wonder | Mach | 3D Rage |

Rage Pro |

Rage 128 |

Radeon 7000 |

Radeon 8000 |

Radeon 9000 |

Radeon X700/X800 |

Radeon X1000 |

Radeon HD 2000 |

Radeon HD 3000 |

Radeon HD 4000 |

Radeon HD 5000 |

Radeon HD 6000 |

Radeon HD 7000 |

Radeon 200 |

Radeon 300 |

Radeon 400/500/600 |

Radeon RX Vega, Radeon VII |

Radeon RX 5000 |

Radeon RX 6000 |

Radeon RX 7000 | |||

| AMD support | ||||||||||||||||||||||||||

| Kind | 2D | 3D | ||||||||||||||||||||||||

| Instruction set architecture | Not publicly known | TeraScale instruction set | GCN instruction set | RDNA instruction set | ||||||||||||||||||||||

| Microarchitecture | TeraScale 1 (VLIW) |

TeraScale 2 (VLIW5) |

|

GCN 1st gen |

GCN 2nd gen |

GCN 3rd gen |

GCN 4th gen |

GCN 5th gen |

RDNA | RDNA 2 | RDNA 3 | |||||||||||||||

| Type | Fixed pipeline[lower-alpha 1] | Programmable pixel & vertex pipelines | Unified shader model | |||||||||||||||||||||||

| Direct3D | — | 5.0 | 6.0 | 7.0 | 8.1 | 9.0 11 (9_2) |

9.0b 11 (9_2) |

9.0c 11 (9_3) |

10.0 11 (10_0) |

10.1 11 (10_1) |

11 (11_0) | 11 (11_1) 12 (11_1) |

11 (12_0) 12 (12_0) |

11 (12_1) 12 (12_1) |

11 (12_1) 12 (12_2) | |||||||||||

| Shader model | — | 1.4 | 2.0+ | 2.0b | 3.0 | 4.0 | 4.1 | 5.0 | 5.1 | 5.1 6.5 |

6.7 | |||||||||||||||

| OpenGL | — | 1.1 | 1.2 | 1.3 | 2.1[lower-alpha 2][33] | 3.3 | 4.5 (on Linux: 4.5 (Mesa 3D 21.0))[34][35][36][lower-alpha 3] | 4.6 (on Linux: 4.6 (Mesa 3D 20.0)) | ||||||||||||||||||

| Vulkan | — | 1.0 (Win 7+ or Mesa 17+) |

1.2 (Adrenalin 20.1.2, Linux Mesa 3D 20.0) 1.3 (GCN 4 and above (with Adrenalin 22.1.2, Mesa 22.0)) |

1.3 | ||||||||||||||||||||||

| OpenCL | — | Close to Metal | 1.1 (no Mesa 3D support) | 1.2+ (on Linux: 1.1+ (no Image support on clover, with by rustiCL) with Mesa 3D, 1.2+ on GCN 1.Gen) | 2.0+ (Adrenalin driver on Win7+) (on Linux ROCM, Linux Mesa 3D 1.2+ (no Image support in clover, but in rustiCL with Mesa 3D, 2.0+ and 3.0 with AMD drivers or AMD ROCm), 5th gen: 2.2 win 10+ and Linux RocM 5.0+ |

2.2+ and 3.0 windows 8.1+ and Linux ROCM 5.0+ (Mesa 3D rustiCL 1.2+ and 3.0 (2.1+ and 2.2+ wip))[37][38][39] | ||||||||||||||||||||

| HSA / ROCm | — | ? | ||||||||||||||||||||||||

| Video decoding ASIC | — | Avivo/UVD | UVD+ | UVD 2 | UVD 2.2 | UVD 3 | UVD 4 | UVD 4.2 | UVD 5.0 or 6.0 | UVD 6.3 | UVD 7 [13][lower-alpha 4] | VCN 2.0 [13][lower-alpha 4] | VCN 3.0 [40] | VCN 4.0 | ||||||||||||

| Video encoding ASIC | — | VCE 1.0 | VCE 2.0 | VCE 3.0 or 3.1 | VCE 3.4 | VCE 4.0 [13][lower-alpha 4] | ||||||||||||||||||||

| Fluid Motion [lower-alpha 5] | ? | |||||||||||||||||||||||||

| Power saving | ? | PowerPlay | PowerTune | PowerTune & ZeroCore Power | ? | |||||||||||||||||||||

| TrueAudio | — | Via dedicated DSP | Via shaders | |||||||||||||||||||||||

| FreeSync | — | 1 2 | ||||||||||||||||||||||||

| HDCP[lower-alpha 6] | ? | 1.4 | 2.2 | 2.3 [41] | ||||||||||||||||||||||

| PlayReady[lower-alpha 6] | — | 3.0 | 3.0 | |||||||||||||||||||||||

| Supported displays[lower-alpha 7] | 1–2 | 2 | 2–6 | ? | ||||||||||||||||||||||

| Max. resolution | ? | 2–6 × 2560×1600 |

2–6 × 4096×2160 @ 30 Hz |

2–6 × 5120×2880 @ 60 Hz |

3 × 7680×4320 @ 60 Hz [42] |

7680×4320 @ 60 Hz PowerColor |

7680x4320

@165 HZ | |||||||||||||||||||

/drm/radeon[lower-alpha 8] |

— | |||||||||||||||||||||||||

/drm/amdgpu[lower-alpha 8] |

— | Experimental [43] | Optional [44] | |||||||||||||||||||||||

- ↑ The Radeon 100 Series has programmable pixel shaders, but do not fully comply with DirectX 8 or Pixel Shader 1.0. See article on R100's pixel shaders.

- ↑ R300, R400 and R500 based cards do not fully comply with OpenGL 2+ as the hardware does not support all types of non-power of two (NPOT) textures.

- ↑ OpenGL 4+ compliance requires supporting FP64 shaders and these are emulated on some TeraScale chips using 32-bit hardware.

- 1 2 3 The UVD and VCE were replaced by the Video Core Next (VCN) ASIC in the Raven Ridge APU implementation of Vega.

- ↑ Video processing for video frame rate interpolation technique. In Windows it works as a DirectShow filter in your player. In Linux, there is no support on the part of drivers and / or community.

- 1 2 To play protected video content, it also requires card, operating system, driver, and application support. A compatible HDCP display is also needed for this. HDCP is mandatory for the output of certain audio formats, placing additional constraints on the multimedia setup.

- ↑ More displays may be supported with native DisplayPort connections, or splitting the maximum resolution between multiple monitors with active converters.

- 1 2 DRM (Direct Rendering Manager) is a component of the Linux kernel. AMDgpu is the Linux kernel module. Support in this table refers to the most current version.

Operating system support

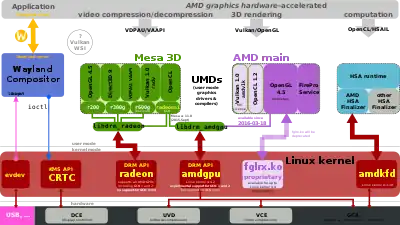

The VCE SIP core needs to be supported by the device driver. The device driver provides one or multiple interfaces, e. g. OpenMAX IL. One of these interfaces is then used by end-user software, like GStreamer or HandBrake (HandBrake rejected VCE support in December 2016,[45] but added it in December 2018[46]), to access the VCE hardware and make use of it.

AMD's proprietary device driver AMD Catalyst is available for multiple operating systems and support for VCE was added to it. Additionally, a free device driver is available. This driver also supports the VCE hardware.

Linux

- Initial VCE support was added on 4 February 2014 by Christian König of AMD to the free radeon driver.[47]

- Gallium3D state tracker for OpenMAX was added 24 October 2013 to Mesa 3D.[48]

- The free and open-source Radeon driver was adapted to use OpenMAX with the GStreamer OpenMAX (gst-omx) support for exposing the VCE video encode engine.[49]

- AMD employee Leo Liu implemented h264 level support into the Mesa 3D state tracker.[50]

Windows

The software "MediaShow Espresso Video Transcoding" seems to utilize VCE and UVD to the fullest extent possible.[51]

XSplit Broadcaster supports VCE from version 1.3.[52]

Open Broadcaster Software (OBS Studio) supports VCE for recording and streaming. The original Open Broadcaster Software (OBS) requires a fork build in order to enable VCE.[53]

AMD Radeon Software supports VCE with built in game capture ("Radeon ReLive") and use AMD AMF/VCE on APU or Radeon Graphics card to reduce FPS drop when capturing game or video content.[54]

HandBrake added Video Coding Engine support in version 1.2.0 in December 2018.[46]

Successor

The VCE was succeeded by AMD Video Core Next in the Raven Ridge series of APUs released in October 2017. The VCN combines both encode (VCE) and decode (UVD).[55]

See also

Video hardware technologies

AMD

- Video Core Next - AMD

- Video Coding Engine - AMD

- Unified Video Decoder - AMD

- Video Shader - ATI

Others

- Intel Quick Sync Video – Intel's equivalent SIP core

- Nvidia NVENC – Nvidia's equivalent SIP core

- Qualcomm Hexagon - Qualcomm's equivalent SIP core

References

- 1 2 "Introducing the Video Coding Engine (VCE) - AMD". developer.amd.com. Archived from the original on 4 June 2016. Retrieved 15 January 2022.

- ↑ "Product brief". amd.com.

- ↑ "Updates" (PDF). amd.com.

- ↑ "White Paper AMD UnifiedVideoDecoder (UVD)" (PDF). 2012-06-15. Retrieved 2017-05-20.

- ↑ "AnandTech Portal | AMD Radeon HD 7970 Review: 28nm And Graphics Core Next, Together As One". Anandtech.com. Retrieved 2014-03-27.

- ↑ "AMD's Radeon HD 7970 graphics processor - The Tech Report - Page 5". The Tech Report. 3 January 2012. Retrieved 2014-03-27.

- ↑ "AMD A-Series APU block diagram". 2011-06-30. Retrieved 2015-01-22.

- ↑ "Video & Movies: The Video Codec Engine, UVD3, & Steady Video 2.0". AnandTech. December 22, 2011. Retrieved 2017-05-20.

- ↑ "Radeon HD 8900 Specs". AMD. Retrieved 2016-07-18.

- ↑ "Mailing Lists". lists.freedesktop.org. 4 June 2015. Retrieved 25 September 2023.

- ↑ "VCEEnc". June 10, 2023 – via GitHub.

- ↑ "Video Encode API: BFrames not supported on RX 4xx? · Issue #8 · GPUOpen-LibrariesAndSDKs/AMF". GitHub.

- 1 2 3 4 Killian, Zak (March 22, 2017). "AMD publishes patches for Vega support on Linux". Tech Report. Retrieved March 23, 2017.

- ↑ Larabel, Michael (20 March 2017). "AMD Sends Out 100 Patches, Enabling Vega Support In AMDGPU DRM". Phoronix. Retrieved 25 August 2017.

- ↑ Deucher, Alex (15 May 2018). "[PATCH 50/57] drm/amdgpu/vg20:Enable the 2nd instance IRQ for uvd 7.2". Retrieved 2019-01-13.

- ↑ Deucher, Alex (15 May 2018). "[PATCH 42/57] drm/amd/include/vg20: adjust VCE_BASE to reuse vce 4.0 header files". Retrieved 2019-01-13.

- ↑ "AMD Announces the 7th Generation APU: Excavator mk2 in Bristol Ridge and Stoney Ridge for Notebooks". 31 May 2016. Retrieved 3 January 2020.

- ↑ "AMD Mobile "Carrizo" Family of APUs Designed to Deliver Significant Leap in Performance, Energy Efficiency in 2015" (Press release). 20 November 2014. Retrieved 16 February 2015.

- ↑ "The Mobile CPU Comparison Guide Rev. 13.0 Page 5 : AMD Mobile CPU Full List". TechARP.com. Retrieved 13 December 2017.

- 1 2 "AMD VEGA10 and VEGA11 GPUs spotted in OpenCL driver". VideoCardz.com. Retrieved 6 June 2017.

- ↑ Cutress, Ian (1 February 2018). "Zen Cores and Vega: Ryzen APUs for AM4 – AMD Tech Day at CES: 2018 Roadmap Revealed, with Ryzen APUs, Zen+ on 12nm, Vega on 7nm". Anandtech. Retrieved 7 February 2018.

- ↑ Larabel, Michael (17 November 2017). "Radeon VCN Encode Support Lands in Mesa 17.4 Git". Phoronix. Retrieved 20 November 2017.

- 1 2 "AMD Ryzen 5000G 'Cezanne' APU Gets First High-Res Die Shots, 10.7 Billion Transistors In A 180mm2 Package". wccftech. Aug 12, 2021. Retrieved August 25, 2021.

- ↑ Tony Chen; Jason Greaves, "AMD's Graphics Core Next (GCN) Architecture" (PDF), AMD, retrieved 13 August 2016

- ↑ "A technical look at AMD's Kaveri architecture". Semi Accurate. Retrieved 6 July 2014.

- ↑ "How do I connect three or More Monitors to an AMD Radeon™ HD 5000, HD 6000, and HD 7000 Series Graphics Card?". AMD. Retrieved 8 December 2014.

- ↑ Airlie, David (26 November 2009). "DisplayPort supported by KMS driver mainlined into Linux kernel 2.6.33". Retrieved 16 January 2016.

- ↑ "Radeon feature matrix". freedesktop.org. Retrieved 10 January 2016.

- ↑ Deucher, Alexander (16 September 2015). "XDC2015: AMDGPU" (PDF). Retrieved 16 January 2016.

- 1 2 Michel Dänzer (17 November 2016). "[ANNOUNCE] xf86-video-amdgpu 1.2.0". lists.x.org.

- ↑ "AMD Radeon HD 6900 (AMD Cayman) series graphics cards". HWlab. hw-lab.com. December 19, 2010. Archived from the original on August 23, 2022. Retrieved August 23, 2022.

New VLIW4 architecture of stream processors allowed to save area of each SIMD by 10%, while performing the same compared to previous VLIW5 architecture

- ↑ "GPU Specs Database". TechPowerUp. Retrieved August 23, 2022.

- ↑ "NPOT Texture (OpenGL Wiki)". Khronos Group. Retrieved February 10, 2021.

- ↑ "AMD Radeon Software Crimson Edition Beta". AMD. Retrieved 2018-04-20.

- ↑ "Mesamatrix". mesamatrix.net. Retrieved 2018-04-22.

- ↑ "RadeonFeature". X.Org Foundation. Retrieved 2018-04-20.

- ↑ "AMD Radeon RX 6800 XT Specs". TechPowerUp. Retrieved January 1, 2021.

- ↑ "AMD Launches The Radeon PRO W7500/W7600 RDNA3 GPUs". Phoronix. 3 August 2023. Retrieved 4 September 2023.

- ↑ "AMD Radeon Pro 5600M Grafikkarte". TopCPU.net (in German). Retrieved 4 September 2023.

- ↑ Larabel, Michael (September 15, 2020). "AMD Radeon Navi 2 / VCN 3.0 Supports AV1 Video Decoding". Phoronix. Retrieved January 1, 2021.

- ↑ Edmonds, Rich (February 4, 2022). "ASUS Dual RX 6600 GPU review: Rock-solid 1080p gaming with impressive thermals". Windows Central. Retrieved November 1, 2022.

- ↑ "Radeon's next-generation Vega architecture" (PDF). Radeon Technologies Group (AMD). Archived from the original (PDF) on September 6, 2018. Retrieved June 13, 2017.

- ↑ Larabel, Michael (December 7, 2016). "The Best Features of the Linux 4.9 Kernel". Phoronix. Retrieved December 7, 2016.

- ↑ "AMDGPU". Retrieved December 29, 2023.

- ↑ "HandBrake rejected VCE pull request". GitHub. 2016-12-08. Retrieved 2017-08-15.

- 1 2 "HandBrake added VCE support in v1.2.0". 2018-12-22. Retrieved 2018-12-31.

- ↑ König, Christian (4 February 2014). "initial VCE support". mesa-dev (Mailing list). Retrieved 28 November 2015.

- ↑ König, Christian (24 October 2013). "OpenMAX state tracker". mesa-dev (Mailing list). Retrieved 28 November 2015.

- ↑ "AMD Open-Sources VCE Video Encode Engine Code". Phoronix. 2014-02-04. Retrieved 2017-05-20.

- ↑ "st/omx/enc: implement h264 level support". 2014-06-12. Retrieved 2017-05-20.

- ↑ "MediaShow Espresso Video Transcoding Benchmark". 2014-01-14. Retrieved 2017-05-20.

- ↑ "XSplit Broadcaster 1.3 maintenance update includes mainly performance enhancements and maintenance fixes including such noteworthy features such as support for AMD's VCE H.264 hardware encoder". Archived from the original on 2014-07-22.

- ↑ "OBS branch with AMD VCE support". May 2, 2014. Retrieved 2017-05-20.

- ↑ "Radeon Software Crimson ReLive Edition 16.12.1 Release Notes". Retrieved 2017-05-20.

- ↑ Larabel, Michael (17 November 2017). "Radeon VCN Encode Support Lands In Mesa 17.4 Git". Phoronix. Retrieved 20 November 2017.