| |

| Designer | Hewlett-Packard |

|---|---|

| Bits | Hybrid 64-bit GPR, 20-bit address bus, 4-bit datapath, 4-bit minimum word size |

| Introduced | 1984 |

| Version | "Level 2" |

| Design | CISC |

| Type | Combination of a load–store architecture with some exceptions which fall into the register–memory architecture family |

| Encoding | Variable |

| Branching | Carry bit, "sticky" bit and other flag registers |

| Endianness | Little-endian |

| Page size | No MMU or paging available |

| Extensions | Only extensions for emulated ARM-based "virtual" CPUs |

| Open | Proprietary |

| Predecessor | Nut |

| Registers | |

| Nine 64-bit GPR and "scratch" registers, two 20-bit "data pointer" registers and other miscellaneous registers | |

| General-purpose | Four 64-bit GPRs |

| Floating point | No FPU registers |

| Vector | No vector registers |

The Saturn family of 4-bit (datapath) microprocessors was developed by Hewlett-Packard in the 1980s first for the HP-71B handheld computer and then later for various HP calculators (starting with the HP-18C). It succeeded the Nut family of processors used in earlier calculators. The original Saturn chip was first used in the HP-71B hand-held BASIC-programmable computer, introduced in 1984. Later models of the family powered the popular HP 48 series of calculators. The HP48SX and HP48S were the last models to use genuine Saturn processors manufactured by HP. Later calculator models used Saturn processors manufactured by NEC. The HP 49 series initially used the Saturn CPU as well, until the NEC fab[nb 1] could no longer manufacture the processor for technical reasons in 2003. Therefore, starting with the HP 49g+ model in 2003, the calculators switched to a Samsung S3C2410 processor with an ARM920T core (part of the ARMv4T architecture) which ran an emulator of the Saturn hardware in software. In 2000, the HP 39G and HP 40G were the last calculators introduced based on the actual NEC fabricated Saturn hardware. The last calculators based on the Saturn emulator were the HP 39gs, HP 40gs and HP 50g in 2006, as well as the 2007 revision of the hp 48gII. The HP 50g, the last calculator utilizing this emulator, was discontinued in 2015 when Samsung stopped producing the ARM processor on which it was based.[1][2][3]

Architecture

The Saturn hardware is a nibble serial design[4] as opposed to its Nut predecessor, which was bit-serial.[5] Internally, the Saturn CPU has four 4-bit data buses that allow for nearly 1-cycle per nibble performance with one or two buses acting as a source and one or two acting as a destination.[4] The smallest addressable word is a 4-bit nibble which can hold one binary-coded decimal (BCD) digit. Any unit of data in the registers larger than a nibble, in which the end of said data unit falls on a nibble boundary and the start of said data unit starts at nibble zero (and also in some cases where said data unit's starting position falls on a nibble boundary with certain register fields eg. "M" or "X"), and which can be up to 64-bits, can be operated on as a whole, but the Saturn CPU performs the operation serially internally on a nibble-by-nibble basis.[4]

The Saturn architecture has a 64-bit data word width and 20-bit address width, with memory being addressed to 4-bit (nibble) granularity. Saturn ALU instructions support variable data width, operating on one to 16 nibbles of a word. The main registers (GPRs), along with the temporary registers, are fully 64-bits wide, but the address registers are only 20-bits wide. The original Saturn CPU chips provided a four-bit external data bus, but later Saturn-based SoCs included on chip bus conversion to an 8-bit external data bus and 19-bit external address bus.

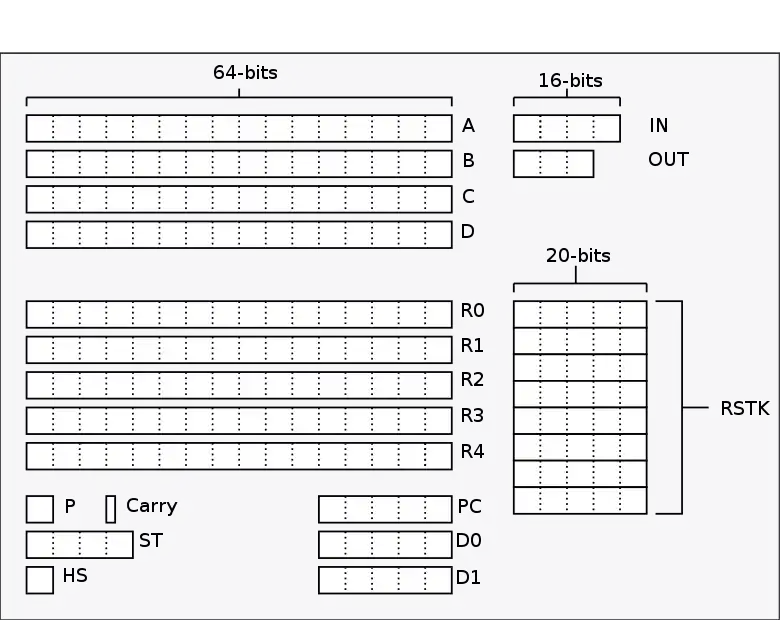

The Saturn architecture has four 64-bit GPRs (General Purpose Registers), named A, B, C and D. In addition, there are also five 64-bit "scratch" registers named R0, R1, R2, R3 and R4. These can only store data. If an ALU operation is required for data in a scratch register, then the register in question must be transferred to a GPR first. Other registers include a 1-nibble "pointer" register named P, usually used to select a nibble in a GPR or a range of nibbles (or for aligning immediate data on a specific nibble in a GPR, with wrap-around). For memory access, there are two 20-bit data pointer registers named D0 and D1. The Saturn architecture also has a PC or program counter register which can interoperate with the GPRs. There is also an 8-level, circular, LIFO 20-bit hardware return stack named RSTK used when a subroutine call instruction is issued. Additionally, the Saturn CPU is equipped with a 16-bit software status register named ST and a 1-nibble hardware status register named HS, which notably, contains the SB or "sticky bit" flag indicating whether a binary 1 was right shifted off of a GPR. Furthermore, the Saturn architecture has a 12-bit OUT register and a 16-bit IN register, which in the Yorke and Clarke SoCs, are used to capture input from the keyboard and also control the beeper. There is also a 1-bit carry flag register.

In addition to the above, the Saturn CPU has a simple, non-prioritized interrupt system. When an interrupt occurs, the CPU finishes executing the current instruction, saves the program counter to the hardware return stack (RSTK) and jumps to address 0x0000Fh, where the preceding value is in nibbles.[4] The CPU also interacts with the keyboard scanning logic directly.

The following diagram depicts the registers (with each white square being 4-bits / a nibble except for the Carry flag, which is 1 bit):

Saturn 64-bit GPR register format and fields:

| Bits | 63–60 | 59–56 | 55–52 | 51–48 | 47–44 | 43–40 | 39–36 | 35–32 | 31–28 | 27–24 | 23–20 | 19–16 | 15–12 | 11–8 | 7–4 | 3–0 | |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Nibble | F | E | D | C | B | A | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| Fields | XS | B | |||||||||||||||

| A | |||||||||||||||||

| S | M | X | |||||||||||||||

| W | |||||||||||||||||

| P=0 | P | ||||||||||||||||

| P=7 | WP | ||||||||||||||||

Data in the general purpose registers can be accessed via fields that fall on nibble boundaries, whereas the scratch registers allow only load and store operations. The fields, as shown in the above diagram, are W (whole 64-bit GPR), A (first 5 nibbles of a GPR), S (most significant nibble of a GPR), XS (nibble 2 of a GPR), M (nibbles 3–14 of a GPR), X (first 3 nibbles of a GPR) and B (first byte of a GPR). In addition, there is the P field which selects a nibble from a GPR based on the P register's 4-bit value. Also, there is the WP field which selects nibbles 0 through the nibble selected in the P register. The 64 bits (16 nibbles) can hold BCD-formatted coded floating point numbers composed of a sign nibble (which is "9" if the number is negative), 12 mantissa digits and a 3-digit 10's complement exponent stored in BCD format (±499).[6] The internal representation of BCD floating point values are a 15-digit mantissa with one sign nibble in one register combined with a 20-bit exponent, in 10's complement format, in another register. The use of BCD instead of straight binary representation is advantageous for calculators as it avoids rounding problems that occur on the binary/decimal conversion.

The Saturn CPU's addresses are also nibble-based. The three pointer registers (including the program counter) and address registers are 20 bits wide. Due to this, the Saturn architecture can address 1 M nibbles or, equivalently, 512 K bytes. Beyond that size (e.g. in the 48GX), bank switching is used.

In both the HP 48S/SX and 48G/GX series, and also such calculators as the HP-28S, HP-27S, HP-42S, HP-32SII and the HP-20S, the Saturn CPU core is integrated as part of a more complex integrated circuit (IC) SoC package, save for the original HP-71B handheld computer and the HP-28C which used a separate chip for the Saturn processor. These packages have code names inspired by the members of the Lewis and Clark Expedition. The code-name of the IC is Clarke in the S/SX, after William Clark, and Yorke in the G/GX, after Clark's manservant. Other Saturn-based ICs, such as those used in the HP-28S, HP-27S, HP-42S, HP-32SII and HP-20S had other code-names. Specifically, the HP-27S, HP-42S and HP-28S SoC was code-named Lewis, after Meriwether Lewis. Other HP calculators such as the HP-32SII and HP-20S had SoCs code-named Sacajawea after Sacagawea and Bert respectively, although the origin of the Bert code-name may be unknown.

Example code

The following is an integer implementation of a BCD decimal square root algorithm in Saturn Jazz / HP Tools assembly syntax:

** In the following A.W is assumed to contain the argument (< 1E14).

** The result (IP(SQRT(A.W))) is in C.W:

SETDEC

ASL W

C=A W

A=A+A W

A=A+A W

A=A+C W

ASR W

C=0 W

P= 13

LC(1) 5

- CSR WP

C=C-1 P

-- C=C+1 P

A=A-C W

GONC --

A=A+C W

CSR W

P=P-1

P=P-1

GONC -

SETHEX

A=C W

Chipsets and applications

The original Saturn CPU gave its name to the entire instruction set architecture. Later chips had their own code names:

| ISA level | Processor code-name | Used in calculator models | Properties |

|---|---|---|---|

| 0[7][8] | Saturn (1LF2) | HP-44A, HP-71B (1984) | |

| 1[7][8] | Saturn (1LK7) | HP-18C (1986), HP-28C (1987), HP-71B | 640 kHz, more instructions |

| 2[7][8] | Bert[9] (1LU7)[9] | HP-10B (1988), HP-20S (1988), HP-21S | 640 kHz, 10 KB ROM, 256 bytes RAM, LCD driver |

| 2[7][8] | Sacajawea[9] (1LR3) | HP-14B, HP-22S, HP-32S (1988), HP-32S+, HP-32SII (1991) | 640 kHz, 16 KB ROM, 512 bytes RAM, LCD driver |

| 2[7][8] | Lewis[9] (1LR2) | HP-17B (1988), HP 17BII (1990), HP-19B (1988), HP 19BII (1990), HP-27S (1988), HP-28S (1988), HP-42S (1988) | 1 MHz, 64 KB ROM, LCD driver, memory controller, IR control, 3 V CMOS |

| 2[7][8] | Clarke[9] (1LT8)[9] | HP 48SX (1990), HP 48S (1991) | 2 MHz, LCD controller, memory controller, UART and IR control, more instructions |

| 2[7][8] | Yorke[9] 00048-80063[10] | HP 38G (1995), HP 38G+ (1998), HP 39G (2000), HP 40G (2000), HP 48GX (1993), HP 48G (1993),[nb 1] HP 48G+ (1998), HP 49G (1999) | 3.68–4 MHz, LCD controller, memory controller, UART and IR control, manufactured by NEC, more instructions, sometimes also known as Saturn 5 platform |

| ? | New-Yorke | HP 48GX prototype | 8 MHz, LCD controller, memory controller, UART and IR control. This was only made as an internal HP prototype and never released in the wild.[11] |

| 2[7][8][nb 2] | Apple series (Big Apple,[9] Mid Apple,[9] Little Apple) | hp 39g+ (2003), HP 39gs (2006), HP 40gs (2006), hp 49g+ (2003), hp 48gII (2003/2007), HP 50g (2006) | Virtual version of the Yorke CPU emulated by members of the 48/75 MHz Samsung S3C2410 processor family with ARM920T core (of the ARMv4T architecture) aka Saturn+ with additional virtual instructions |

The CPU code-names are inspired by members of the Lewis and Clark Expedition of 1804–1806, the first United States overland expedition to the Pacific coast and back. The virtual CPU / emulator code names were inspired by the prototype "New-Yorke" Saturn-based 8 MHz SoC that never made it to production.[12] According to one of the ACO (Australian Calculator Operation) members, "Big Apple" was derived from the code name "New-Yorke" of the prototype 8 MHz Saturn-based SoC, and which to the original author, seemed to intimate a reference to "New York" the city, hence the names "Big apple", "Mid Apple" and "Little Apple".[12]

See also

Notes

References

- ↑ Kuperus, Klaas (2015-03-04). "HP 50g: End of an era". forum.hp-prime.de. Moravia. Archived from the original on 2015-04-02.

- ↑ Kuperus, Klaas (2015-03-06). "HP 50g not so good news?". HP Museum. Moravia. Archived from the original on 2018-07-08. Retrieved 2016-01-01.

- ↑ Wessman, Timothy "Tim" James (2015-12-26). "Windows 10 won't allow HP 50g USB drivers to be installed". HP Museum. Archived from the original on 2018-07-08. Retrieved 2016-01-01.

- 1 2 3 4 HP-71B Hardware Internal Design Specification Vol 1. Hewlett Packard Corporation. September 1984. p. 3-1.

- ↑ HP-41C CPU, Display Driver, HP-IL, Data Storage, Timer IC, and Interface IC Specifications. Hewlett Packard Corporation. July 1981. p. 5.

- ↑ Fernandes, Gilbert Henri (2005-07-16) [1999-01-29]. "Chapter 56.1 Real number". In Rechlin, Eric (ed.). Introduction to Saturn Assembly Language (3rd ed.). hpcalc.org. p. 104. ID 1693. Archived from the original on 2018-11-13. Retrieved 2019-04-29.

If the exponent is negative, the exponent is encoded as "1000 - ABS(exponent)"

- 1 2 3 4 5 6 7 8 Donnini, Giuseppe (2020-06-26). ""New-Yorke" ?". www.hpmuseum.org. Retrieved 2020-07-06.

- 1 2 3 4 5 6 7 8 "The Saturn assembler manual". www.hpcalc.org. Hewlett Packard. 1993-08-20. Retrieved 2020-07-06.

- 1 2 3 4 5 6 7 8 9 Finseth, Craig A. (2016-12-23). "names". Archived from the original on 2017-12-21. Retrieved 2017-12-21.

- ↑ Arnett, Dave (1994-05-03). "Name that chip!". Newsgroup: comp.sys.hp48. Archived from the original on 2019-04-29. Retrieved 2019-04-22.

- ↑ de Brébisson, Cyrille (2020-06-17). "RE: "New-Yorke" ?". www.hpmuseum.org. Retrieved 2020-06-18.

- 1 2 de Brébisson, Cyrille (2020-06-16). "RE: "New-Yorke" ?". www.hpmuseum.org. Retrieved 2020-06-18.

Further reading

- Mastracci, Matthew (1998) [1995]. "Guide to the Saturn Processor (With HP48 Applications)". 1.0b. Archived from the original on 2016-08-06. Retrieved 2006-05-03.

- Courbis, Paul; Lalande, Sébastien (2006-06-27) [1989]. Voyage au centre de la HP28c/s (in French) (2 ed.). Paris, France: Editions de la Règle à Calcul. OCLC 636072913. Archived from the original on 2016-08-06. Retrieved 2015-09-06.

- Courbis, Paul; Lalande, Sébastien (2006-06-25) [1993]. HP48 Machine Language - A Journey to the Center of the HP 48s/sx. Translated by Cannon, Douglas R. (2nd ed.). Corvallis, Oregon, USA: Grapevine Publications, Inc. OCLC 34148948. Archived from the original on 2018-11-14. Retrieved 2015-09-06.

- Courbis, Paul; Lalande, Sébastien (2006-06-25) [1991]. Voyage au centre de la HP48 s/sx. 3.02 (in French) (3rd ed.). Paris, France: Editions Angkor. ISBN 2-87892-003-1. OCLC 29640044. Archived from the original on 2018-11-13. Retrieved 2015-09-06.

- Courbis, Paul (2006-06-25) [1993]. Voyage au centre de la HP48 g/gx. 3.05 (in French) (3rd ed.). Paris, France: Editions Angkor. ISBN 2-87892-006-6. OCLC 29640044. Archived from the original on 2016-08-06. Retrieved 2015-09-06.

- Courbis, Paul; de Brébisson, Cyrille (March 1994). Le compagnon de Voyage de la HP48 G/GX (in French). Paris, France: Editions Angkor. ISBN 2-87892-007-4. Archived from the original on 2016-08-06. Retrieved 2015-09-06.

- Fernandes, Gilbert Henri (2005-07-16) [1999-01-29]. Rechlin, Eric (ed.). Introduction to Saturn Assembly Language (3rd ed.). hpcalc.org. ID 1693. Archived from the original on 2016-08-06. Retrieved 2009-02-17.