扇出晶圆级封装

扇出晶圆级封装(FOWLP)是一种集成电路封装技术,是标准晶圆级封装(WLP)技术的强化。 [1] [2]

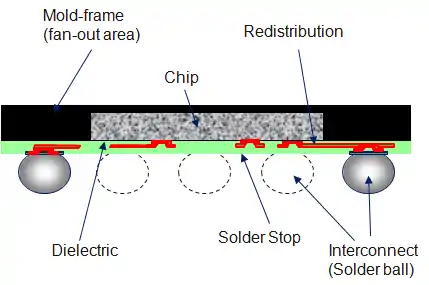

嵌入式晶圆级球阵列封装(eWLB)草图,第一个商业化FOWLP技术

传统技术中,首先对晶圆进行切割,然后对单个裸晶進行封裝。封裝尺寸通常比晶片尺寸大得多。相比之下,在標準WLP流程中,集成电路在仍处于晶圆时进行封装,然后附有封装外层的晶圆才被切割;最终的封装实际上与芯片本身尺寸相同。然而,小封裝限制了有限封裝空間可容納的外部接點。對於需要大量接觸的複雜半導體裝置則可能成為重大限制。

FOWLP的開發就是為了放寬這個限制。與傳統封裝相比,它提供了更小的封裝尺寸、改進的熱性能和電氣性能,並且允許在不增加晶片尺寸的情況下提高觸點數量。

與標準WLP流程相反,FOWLP中,首先對晶圓進行切割,切割出來的晶片會非常精確地重新定位在載體晶圓或面板上,並在每個晶片周圍保留扇出空间。然后通过模塑來重構載體,然後在整個模製區域頂部(晶片頂部和相鄰扇出區域頂部)製作重布线層,然后在顶部形成焊球。

历史

FOWLP技术最开始由英飞凌开发,台积电以此技术为基础,生产A10处理器。[3]

FOWLP可使用“先芯片(die first)”,裸片面朝下或面朝上安装;或者“后芯片(die last)”方式组装而成。面朝下的方法免于制造铜柱及背面研磨的步骤,制造成本低,但存在裸片移位、晶圆翘曲等问题。面朝上的方法,由于芯片背面完全暴露,利于散热。而后芯片的优点在于制造过程中可以使用验证合格的裸片(known good die,KGD),提高良率。[4]

优点

FOWLP不仅消除了芯片互连和基板,实现了更好的电气性能,降低更低,还在提供了更精细的线路和空间,从而实现更好的可布线性。此外,由于FOWLP使用类似晶圆厂的工艺,产量远高于嵌入式有机基板层压技术,然而,当在器件上构建基板时,工艺必须足够稳健,才能实现>99.5% 的良率;否则基板和封装都会报废。有机层压基板工业工艺、材料和设备的设计初衷并不是为了提供如此高的产量。 然而,嵌入式相对于FOWLP,因为不使用高端晶圆厂工艺或材料,成本较低。[5]

参考

- Korczynski, Ed. . Semiconductor Manufacturing & Design Community. 2014-05-05 [2018-09-24]. (原始内容存档于2018-08-16).

- . Orbotech. n.d. [2018-09-24]. (原始内容存档于2018-09-22).

- . www.zhihu.com. [2024-01-07].

- . www.eet-china.com. [2024-03-25].

- Keser, Beth (编). . Wiley http://dx.doi.org/10.1002/9781119313991. 2019-01-18. ISBN 978-1-119-31413-4. 缺少或

|title=为空 (帮助)

外部链接

This article is issued from Wikipedia. The text is licensed under Creative Commons - Attribution - Sharealike. Additional terms may apply for the media files.