Nehalem微架構

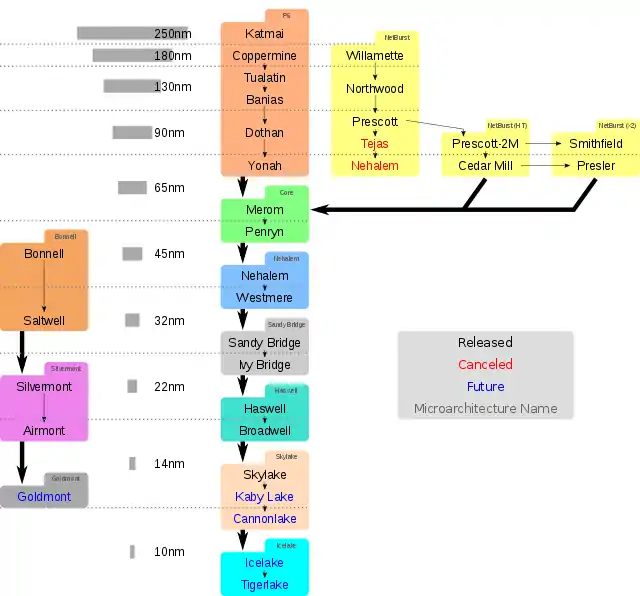

Intel Nehalem (發音:/nəˈheɪləm/[1]) ,是Intel研發的中央處理器微架構之代號,該架構取代了前代的Core微處理器架構。[2] 使用Nehalem架構的微處理器採用45納米製程(後期改用32納米製程),在2007年的Intel開發者論壇上Intel官方展示了一個採用兩顆Nehalem微架構的處理器的系統平台。首款採用Intel Nehalem架構的處理器是2008年11月正式發售的桌上型處理器Intel Core i7。[3]

| 產品化 | 2008年11月11日 |

|---|---|

| 設計團隊 | Intel |

| 生产商 | |

| 指令集架構 | MMX、SSE、SSE2、SSE3、 SSSE3、SSE4.1、SSE4.2、x86、 x86-64、EM64T、EIST、 XD bit、AES |

| 制作工艺/製程 | 45nm |

| 核心数量 | 2 個至 8 個 |

| 一級快取 | 64KB(每核心) |

| 二級快取 | 256KB(每核心) |

| 三級快取 | 4MB~12MB(各核心共享) |

| CPU主频范围 | 至 3.33 GHz |

| QPI速率 | 4.8 GT/s 至 6.4 GT/s |

| DMI速率 | 2.5 GT/s 至 5.0 GT/s |

| CPU插座 | |

| 封裝 | |

| 應用平台 | 伺服器、工作站、桌上型電腦、筆記型電腦、超級計算機 |

| 核心代號 |

|

| 使用的處理器型號 | |

| 上代產品 | Core |

| 繼任產品 | Westmere |

Intel在Pentium 4時代也使用過“Nehalem”的代號,該代號曾使用於NetBurst微架構的10Ghz版本之Pentium 4微處理器,後來改計劃取消。Nehalem微架構儘管與Netburst架構不是同一個時代的產物,但是兩者之間有一些共同的技術和特點,如超執行緒、較高的預設時脈等。儘管Nehalem架構的微處理器預設時脈普遍較高,但能效比依然比Core微架構的製程改進版Penryn微架構的微處理器要高。2011年1月,Intel Nehalem微架構由其下一代微架構Intel Sandy Bridge所取代。

Intel Nehalem的架構設計有不少地方與AMD K10類似(譬如每核心獨立電壓及時脈等),但要比AMD K10的效能更佳、能耗更低。AMD後來也推出K10的改進版K10.5來與Intel的Nehalem競爭。

技術特點

整合北橋

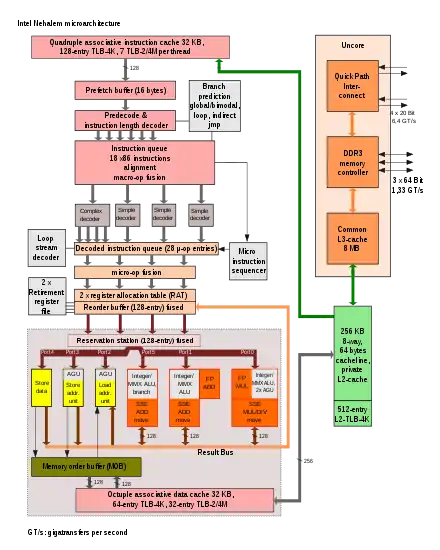

全部型號的微處理器核心都整合了記憶體控制器,一般支援雙通道DDR3 SDRAM,消費級產品最高支援三通道DDR3 SDRAM,而伺服器平台則可以支援四通道DDR3 SDRAM;除此以外還處理器核心還整合了PCI Express 2.0控制器。

直連式總線

從Nehalem微架構開始,Intel改用QPI/DMI直連式總線,放棄了傳統的FSB。首發的Core i7使用了新的“Quick Path Interconnect”直連式總線,與AMD的HyperTransport相似。

相比FSB,每一個處理器都可以有獨立的QPI通道與其他處理器連接,處理器之間不用再共享FSB頻寬,並繞路到北橋才能通訊。此外,QPI是雙向傳輸[4]。

後來發布的Core i5、i3,處理器內部仍使用QPI,但與外部晶片組連接則使用與QPI類似但較QPI的頻寬小的DMI(Direct Media Interface)總線。

隨著FSB的『卸任』,一般意義上的『外頻』概念由『基準時鐘頻率』(BLCK)所取代。[5]

模組化的多核心設計

處理器採用模組化設計[6]。例如核心、記憶體控制器、以至輸入輸出介面控制器,都能夠以不同的數量配搭,而且都能做到原生多核心設計。這樣使得Nehalem架構的處理器產品線可以做成雙核心、四核心、六核心乃至八核心、十核心(僅見於Xeon E7)[7],可以使到產品更容易針對不同市場。與AMD K10微架構類似,每一個模組都可以有獨立的電壓和獨立的時脈,讓處理器在不同負載水平的效能最大化的同時更省電。

超執行緒

超執行緒技術回歸:部分處理器型號支援超线程的技術。消費級市場發售的最高六核心,十二執行緒,企業級的更達到八核心,十六執行緒甚至到後期的十核心,二十執行緒。不僅多執行緒處理能力加強,Intel認為該技術還能最多提升處理器30%的效能。

快取

多級快取:每核心64KB的L1快取(32KB指令快取+32KB資料快取);每核心256KB的L2快取,雖容量大小較Core微架構的小但擁有更低的讀寫延遲值;與AMD K10一樣,Intel Nehalem微架構的處理器都內建L3快取,每一個處理器共享最小4MB至最大12MB(企業級處理器更達到30MB)。

效能、電源管理

效能動態調節和電源管理:中高階型號的處理器會支援Turbo Boost(港澳地區沒有正式官方中文名稱,台灣官方中文名稱為『渦輪加速』,中國大陸官方中文名稱為『睿頻』。其後該技術更名為Dynamic Speed,動態時脈[8])動態時脈調整技術,倘若有程式使用較多的處理器负载,處理器的頻率可以按步驟提升,此外,可以自動往上提升倍頻[9]該功能基本不需要作業系統的支援,完全由硬體監控[10]。除了時脈管理,電源管理方面引入Power Gates技術,核心閒置的時候可被關閉。對比上一代的Core架構,的核心電阻可以被關閉,電流可以完全不通過核心。各個處理器核心可運作於不同的頻率和電壓[11]。Turbo Boost及Power Gates功能都是由同一個單元提供,佔去大約一百萬個晶体管[12]。而AMD K10及後來的改進版K10.5,核心必須手動才能關閉。

指令集

指令集更新:SIMD指令SSE4的版本會提升為SSE 4.2,SSE4.2在SSE4.1(於Core架構上)的基礎上新增了7條指令[13];引入第二代Intel虛擬化技術,支援EPT(Extended Page Table,擴展分頁表)、VPIDs(virtual processor identifiers,虛擬處理器標識)以及非屏蔽中斷窗口退出(non-maskable interrupt-window exiting)。[14]Intel Nehalem架构的原子操作延时降低了50%,在试图限制原子的开销上。[15]

搭配晶片組

晶片組方面,Intel推出了5系列晶片組與之搭配,桌面平台有P5*、H5*、X5*等系列型號,其中P5*、H5*系列型號採用LGA1156插座,X5*採用LGA1366插座。代號Bloomfield的Core i7和後期第二批的Intel X58晶片組(允許更變倍頻)的組合再次提升Intel平台的超頻極限。核心代號Lynnfield的Core i5所使用的晶片組,更名為“PCH”(Platform Controller Hub,PCH,整合了一部分北橋和整個南橋),取代以往分離的北橋晶片和南橋晶片,成為單晶片組。[16]早期,處理器核心的電壓與系統記憶體同步。此前,Intel官方表示首批處理器產品會支持DDR3-800和DDR3-1066規格的記憶體。對於DDR3-1333,由於處理器只可以接受較低的電壓水平(限制在1.65V或以下),高速的記憶體意味著需要較高的電壓,所以此規格的官方支援仍然存在疑問[17]。後來第二批X58晶片組主機版上,處理器核心電壓與系統記憶體電壓可以實現異步,方便用家超頻[18]。另外,原先只有XE版本處理器可以調整記憶體頻率。後來Intel修改為所有上市的Core i7處理器,均可以修改記憶體和QPI總線的頻率[19]。

效能和能耗之改進

儘管核心面積比Core架構要大不少,性能較Core架構系列則仍大幅提升,並沒有令市場期望失望。[20]

與Core架構的45納米製程版本Core相比,Nehalem架構:

- 在相同的能耗下比Core架構的單執行緒效能高出10%至100%;

- 同樣的效能下的能耗平均比Core架構的低30%;

- 每核心每時鐘週期的效能平均比上代架構高12%至20%。

核心及其步進

| 核心數量(記憶體通道數量、其他總線) | 製程 | 晶片面積 | CPUID | Model | 步進 | 流動平台 | 桌面平台、 UP Server | DP Server | MP Server |

|---|---|---|---|---|---|---|---|---|---|

| 八核心(四通道) | 45 nm | 684 mm² | 206E6 | 46 | D0 | Beckton (80604) | |||

| 四核心(三通道) | 45 nm | 263 mm² | 106A4 106A5 | 26 | C0 D0 |

Bloomfield (80601) | Gainestown (80602) | ||

| 四核心(雙通道、PCIe) | 45 nm | 296 mm² | 106E4 106E5 | 30 | B0 B1 |

Clarksfield (80607) | Lynnfield (80605) | Jasper Forest (80612) | |

| 雙核心(雙通道、PCIe、內建顯示核心) | 45 nm | Auburndale (已取消) | Havendale (已取消) | ||||||

| 十核心(四通道)[21] | 32 nm | 513 mm² | 206F2 | 47 | A2 | Westmere-EX (80615) | |||

| 六核心(三通道) | 32 nm | 248 mm² | 206C2 | 44 | B1 | Gulftown (80613) | Westmere-EP (80614) | ||

| 雙核心(雙通道、PCIe、內建顯示核心) | 32 nm 45 nm | 81+114 mm² | 20652 20655 | 37 | C2 K0 |

Arrandale (80617) | Clarkdale (80616) | ||

- 極致效能級別的處理器無倍頻限制;

- 全部微處理器使用133MHz的基準時鐘頻率。

處理器列表

繼任微架構

Intel遵循Tick-Tock策略,於2011年第一季度發布了Intel Sandy Bridge微架構,正式取代Intel Nehalem微架構以及其製程改進版Intel Westmere微架構。

參考

- , [2012-04-30], (原始内容存档于2011-12-10)

- , Intel Corporation, 2007-03-28 [2012-04-30], (原始内容存档于2009-02-20)

- Gruener, Wolfgang, , TG Daily, 2008-08-10 [2012-04-30], (原始内容存档于2009-08-14)

- . [2012-04-30]. (原始内容存档于2012-04-30).

- 又能超外频了? Haswell或恢复FSB概念 (页面存档备份,存于) - zol.com.cn

- . [2012-04-30]. (原始内容存档于2012-01-14).

- . [2012-06-27]. (原始内容存档于2011-12-17).

- . [2012-04-30]. (原始内容存档于2008-09-20).

- . [2012-04-30]. (原始内容存档于2008-12-03).

- . [2012-04-30]. (原始内容存档于2012-04-13).

- . [2012-04-30]. (原始内容存档于2012-01-14).

- . [2012-04-30]. (原始内容存档于2012-01-22).

- . [2012-04-30]. (原始内容存档于2009-08-17).

- . [2012-04-30]. (原始内容存档于2012-03-13).

- , [2012-04-30], (原始内容存档于2012-05-11)

- Botezatu, Bogdan, , Softpedia, 2008-04-22 [2012-04-30], (原始内容存档于2012-01-18)

- . [2012-04-30]. (原始内容存档于2012-01-14).

- . [2012-04-30]. (原始内容存档于2012-01-14).

- . [2012-04-30]. (原始内容存档于2009-02-26).

- , PC Watch, 2008-01-29 [2012-04-30], (原始内容存档于2012-03-08)

- . [2012-06-03]. (原始内容存档于2012-03-16).

外部連結

- Nehalem processor(页面存档备份,存于) at Intel.com

- , InfoWorld, 2010-03-16 [2012-05-01], (原始内容存档于2011-01-09)

- , X-bit Labs, 2009-09-24 [2012-05-01], (原始内容存档于2011-03-08)

- , Hot Hardware, 2008-11-03 [2012-05-01], (原始内容存档于2009-03-06)

- , hardCOREware.net, 2008-11-03 [2012-05-01], (原始内容存档于2008-11-06)

- , PC Perspective, 2008-11-03 [2012-05-01], (原始内容存档于2008-11-06)

- , Xtreview, 2008-10-01 [2012-05-01], (原始内容存档于2012-03-09)

- Altavilla, Dave, , HotHardware, 2008-03-17 [2012-05-01], (原始内容存档于2012-05-23)

- Shrout, Ryan, , PC Perspective, 2008-03-28 [2012-05-01], (原始内容存档于2010-05-14)

- Stokes, Jon, , Ars Technica, 2007-03-28 [2012-05-01], (原始内容存档于2009-01-25)

- Lal Shimpi, Anand, , AnandTech, 2007-09-18 [2012-05-01], (原始内容存档于2010-03-06)

- Lal Shimpi, Anand, , AnandTech, 2008-11-03 [2012-05-01], (原始内容存档于2012-09-18)

- David Kanter. . realworldtech.com. 2010-04-04 [2010-12-16]. (原始内容存档于2010-12-21).

- Holland, Maggie, , IT Pro, 2007-09-19 [2012-05-01], (原始内容存档于2007-10-18)

- , CHW.net, 2008-01-05 [2012-05-01], (原始内容存档于2008-07-05) (西班牙语)

- Stokes, Jon, , Ars Technica, 2008-04-09 [2012-05-01], (原始内容存档于2008-11-21)

- Torres, Gabriel, , Hardware Secrets, 2008-03-17 [2012-05-01], (原始内容存档于2008-05-16)

- Shimpi, Anand Lal, , AnandTech, 2008-06-05 [2012-05-01], (原始内容存档于2010-01-04)

- Shimpi, Anand Lal, , AnandTech, 2008-08-21 [2012-05-01], (原始内容存档于2010-01-04)

- , X-bit Labs, 2008-11-02 [2012-05-01], (原始内容存档于2008-11-06)

| 维基共享资源中相关的多媒体资源:Nehalem微架構 |