GS464E

龙芯 GS464E 微架构是龙芯中科的微架构,是上一代龙芯 GS464 微架构的继承者。GS464E微架构为龙芯3A/B2000、龙芯3A/B3000所使用的微架构,两者分别用 40nm 和 28nm 工艺制造。龙芯中科于2015年8月18日正式发布使用该微架构的处理器。[1][2][3][4]

| 推出年份 | 2015年8月18日 |

|---|---|

| 推出公司 | 龙芯中科 |

| 設計團隊 | 龙芯中科总部 |

| 生产商 | |

| 指令集架構 | LoongISA1.0 |

| 制作工艺/製程 | 40nm 至 28nm |

| 核心数量 | 4个 |

| 一級快取 | 128KiB(每核心)(64KiB指令+64KiB数据) |

| 二級快取 | 256KiB(每核心)(受害者缓存) |

| 三級快取 | 最多8MiB(共享) |

| CPU主频范围 | 0.8 GHz 至 1.5 GHz |

| 封裝 | |

| 應用平台 | 台式机、笔记本、工作站、服务器等 |

| 使用的處理器型號 |

|

| 上代產品 | GS464微架构 |

| 繼任產品 | GS464V微架构 |

架构设计

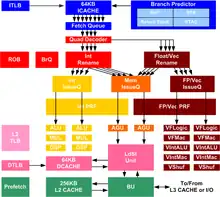

GS464E微架构结构图(一)

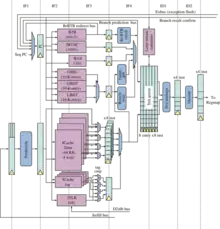

GS464E微架构结构图(二)

GS464E取指部件流水线图

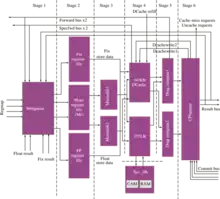

GS464E访存部件流水线图

架构设计特点如下:

- MIPS64 兼容,支持龙芯扩展指令集LoongISA1.0;

- 四发射超标量结构,两个算術邏輯單元(ALU)、两个浮点运算器(FPU)、两个地址生成单元(AGU);

- 每个浮点部件都支持全流水 64 位/双 32 位浮点乘加运算;

- 访存部件支持 128 位存储访问,虚地址为 64 位,物理地址为 48 位;

- 支持寄存器重命名、动态调度、转移预测等乱序执行技术;

- 64 项全相联外加 8 路组相连 1024 项,共计 1088 项 TLB,64 项指令 TLB,可变页大小;

- 和大小各为 64KB,4 路组相联;

- 受害者缓存作为私有二级 Cache,大小为 256KB,16 路组相连;

- 支持 Non-blocking 访问及 Load-Speculation 等访存优化技术;

- 支持缓存一致性协议,可用于片内多核处理器;

- 指令缓存实现奇偶校验,数据缓存实现 ECC 校验;

- 支持标准的 EJTAG 调试标准,方便软硬件调试;

- 标准的 128 位 AXI 接口。

参考文献

This article is issued from Wikipedia. The text is licensed under Creative Commons - Attribution - Sharealike. Additional terms may apply for the media files.