低壓差穩壓器

低壓差穩壓器(英語:,),又稱低壓差線性穩壓器、低壓降穩壓器,是線性直流穩壓器的一種,用途同是提供穩定的直流電壓電源。相比於一般線性直流穩壓器,低壓差穩壓器能於更小輸出輸入電壓差的情況下工作。

歷史

第一個低壓降穩壓器是輸出可調式設計,在1977年發表於雜誌"Electronic Design",題為"Break Loose from Fixed IC Regulators"。該文章作者是Robert Dobkin,當時他任職於美國國家半導體(英語:),該公司因此聲稱是低壓降穩壓器的發明者。[1]Dobkin其後在1981年離開National Semiconductor並與Robert J. Widlar 一起創立Linear Technology,現為該公司的CTO。[2]

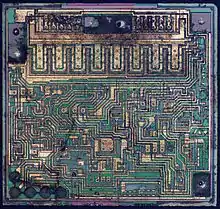

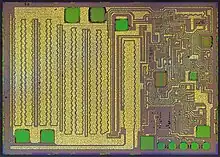

首枚低壓降穩壓器集成電路是LT1083。

原理

低壓差穩壓器原理上與一般的線性直流穩壓器基本相同,分別在於低壓差穩壓器輸出端的功率由NPN 電晶體 共集極架構,改為PNP 集電極開路架構(以使用雙極性晶體管以言)。[3]這種架構下,功率晶體管的控制極只要利用對地的電壓差就能讓晶體管處於飽和導通狀態,因此輸入端只需高出輸出端多於功率晶體管的飽和電壓,穩壓器就能運作,穩定輸出電壓。

這類設計在保持穩定性方設計難度較高,因為輸出級的阻抗較大,較易不穩定或起振。[4]

規格/參數

.jpg.webp)

低壓差穩壓器樣重要的參數有壓降電壓、壓差(Dropout voltage)、靜態耗電電流、靜態電流(quiescent current)、負載調節( Load Regulation ),線性調節(Line Regulation),最大輸出電流,速度,瞬態響應(Transient response)…等。個別低壓差穩壓器會標明電源抑制比(PSRR),輸出噪聲(Output noise)。

壓降電壓/壓差(dropout voltage)

Dropout voltage 是 LDO Regulator 固有的特性,其定義為LDO Regulator 仍能保持輸出穩壓狀態之輸入電壓與輸出電壓的最小壓差,此壓差臨界點(dropout point)發生在輸入電壓非常接近輸出電壓時,當輸入電壓值低於壓差臨界點時,LDO Regulator 即開始不在穩壓狀態

靜態電流(quiescent current)

靜態電流,即穩壓器自身消耗的電流,也就是穩壓器內部的耗電量,測量方法是輸入電流減去輸出電流:

一般低壓差穩壓器的靜態電流都相當低,這使得壓差穩壓器可以長時間處於備用狀態而有不會有明顯電力損耗。低壓差穩壓器的功耗為:

參考文獻

- LDOs, Low Dropout Regulators, Linear Regulators, CMOS Linear Regulator

- . Internet FAQ Consortium. August 19, 2010 [2010-08-25]. (原始内容存档于2018-03-01).

- (PDF). [2016-03-28]. (原始内容 (PDF)存档于2013-02-22).

- (PDF). [2016-03-28]. (原始内容存档 (PDF)于2015-04-04).

- Simpson, Chester. (PDF). ti.com. Texas Instruments. [18 June 2015]. (原始内容存档 (PDF)于2016-03-03).

- Pithadia, Sanjay. (PDF). Texas Instruments. [2016-03-28]. (原始内容 (PDF)存档于2012-10-22).

LDO (Low Dropout Linear Regulator) Introduction(页面存档备份,存于)

LDO 的特性(页面存档备份,存于)