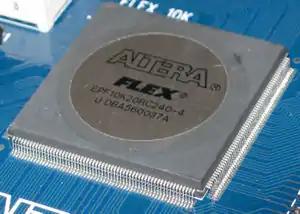

现场可编程逻辑门阵列

現場可程式化邏輯閘陣列(英語:,縮寫為FPGA),它以PAL、GAL、CPLD等可编程逻辑器件為技術基礎發展而成。作為特殊应用集成电路中的一种半定制电路,它既彌補全定制電路不足,又克服原有可编程逻辑控制器邏輯閘數有限的缺點。

概要

目前以硬體描述語言(Verilog或VHDL)描述的逻辑電路,可以利用逻辑合成和布局、布线工具软件,快速地燒錄至FPGA上進行測試,这一过程是現代集成电路设计验证的技術主流。这些可编程逻辑元件可以被用来实现一些基本的邏輯閘数字电路(比如与门、或门、异或门、非门)或者更复杂一些的组合逻辑功能,比如译码器等。在大多数的FPGA里面,这些可编辑的元件里也包含記憶元件,例如正反器(Flip-flop)或者其他更加完整的記憶塊,从而构成时序逻辑电路。

系统设计师可以根据需要,通过可编辑的连接,把FPGA内部的逻辑块连接起来。这就好像一个电路试验板被放在了一个芯片裡。一个出厂后的成品FPGA的逻辑块和连接可以按照设计者的需要而改变,所以FPGA可以完成所需要的逻辑功能。

FPGA一般来说比特殊應用積體電路(ASIC)的速度要慢,无法完成更复杂的设计,并且会消耗更多的电能。但是,FPGA具有很多优点,比如可以快速成品,而且其内部逻辑可以被设计者反复修改,从而改正程序中的错误,此外,使用FPGA进行除錯的成本较低。厂商也可能会提供便宜、但是编辑能力有限的FPGA产品。因为这些芯片有的可编辑能力较差,所以这些设计的开发是在普通的FPGA上完成的,然后将设计转移到一个类似于专用集成电路的芯片上。在一些技术更新比较快的行业,FPGA几乎是电子系统中的必要部件,因为在大批量供货前,必须迅速抢占市场,这时FPGA方便灵活的优势就显得很重要。

與CPLD的比較

为了达到上述目的,另一种方法是采用複雜可程式邏輯裝置(CPLD)而不是FPGA。

早在1980年代中期,FPGA已经在可程式邏輯裝置设备中扎根。CPLD和FPGA都包括了一些相对大数量的可以编辑逻辑单元。CPLD逻辑门的密度在几千到几万个逻辑单元之间,而FPGA通常是在几万到几百万。

CPLD和FPGA的主要区别是他们的系统结构。CPLD的结构具有一定的局限性。这个结构由一个或者多个可编辑的结果之和的逻辑组列和一些相对少量的锁定的寄存器组成。这样的结果是缺乏编辑灵活性,但是它的优点是,其延迟时间易于预计,逻辑单元对连接单元比率较高。而FPGA具有的连接单元数量很大,这样虽然让它可以更加灵活的编辑,但是结构却复杂得多。

CPLD和FPGA另外一个区别是大多数的FPGA含有高层次的内置模块(比如加法器和乘法器)和内置的存储器。一个由此带来的重要区别是,很多新的FPGA支持完全的或者部分的系统内重新配置。允许他们的设计随着系统升级或者动态重新配置而改变。一些FPGA可以让设备的一部分重新编辑,而其他部分继续正常运行。

基本組成

- 静态随机存取存储器(SRAM) - 基於靜態記憶體static memory技術。系統內可程式化和再程式化(re-programmable)。須要外部啟動元件(external boot devices)。 CMOS。

- 反熔丝 - 可燒錄一次。通常為CMOS。

- PROM(一次性可编程EPROM) - 可程式化唯讀記憶體技術,可燒錄一次。使用塑料封裝,無窗,不能清除內容。

- EPROM - 可清除可程式化唯讀記憶體技術,有窗,經紫外線照射可清除內容。

- EEPROM - 可電氣清除可程式化唯讀記憶體技術,可用電氣訊號清除內容。

- 闪存 - 一种特殊的EEPROM。

- 熔丝 - 可燒錄一次。通常為双极性的。不能清除内容。