计数器

在逻辑代数与電腦運算中,计数器是存储(有时还有显示)特定事件或过程发生次数的装置,往往与定時器訊號有关联。最常见的类型是有“时钟”输入线和多输出线的时序逻辑电路。输出线的值代表在二进制或BCD计数系统的数。每个施加到时钟输入的脉冲都会使计数器增加或是減少。

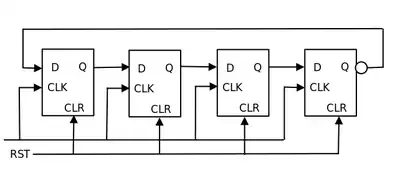

计数器电路通常由多个触发器级联连接而成。计数器在数字电路中使用非常广泛,會制成集成电路芯片以及作为更大集成电路的一部分。

电子计数器

在电子学中,可以用像触发器等寄存器型电路來实现计数器,也存在各种类型:

- 异步(纹波)计数器 – 改变状态位用作后续状态触发器的的时钟

- 同步计数器 – 所有状态位都在单一时钟的控制下

- 十进制计数器 – 每级经过10个状态

- 递增/递减计数器 – 藉由输入信號的控制,可以讓计数器递增或是递减

- 环形计数器 – 由移位寄存器組成,但有額外连接成环狀的反馈電路

- 约翰逊记数器 – 扭环形计数器

- 级联计数器

- 模数计数器。

每种计数器都有不同的用途。计数器在其本質上是数字系统,用二进制计数。不過许多类型的计数器电路可作为数字電路的基本模組,例如4000系列芯片中实现的不同计数器。

有時使用计数序列而不使用自然二进制序列會比較方便—如BCD计数器、线性反馈移位寄存器及格雷码计数器。

计数器用于数字时钟和计时器中,出现在烤箱定时器以及VCR时钟等内部。[1]

异步(纹波)计数器

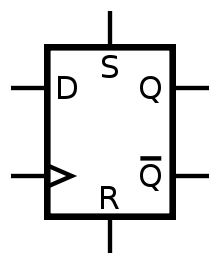

最簡單的异步(纹波)计数器是一個將反向输出反馈给D输入的D型触发器。该电路可以存储一个比特,因此在它溢出(从0重新开始)之前可以从零计数到一。该计数器每个时钟周期会递增一次,两个时钟周期会溢出,故每个周期会从0转换到1,再从1转换到0。异步计数器會產生一個新的新时钟,频率是输入时钟频率的一半,占空比50%。

如果这个输出再接到D型触发器(其反向输出也反馈给D输入)作為時鐘,将会得到计数速度为其一半的另一个1位计数器。把它们整合在一起,就产生了两位计数器:

| 周期 | Q1 | Q0 | (Q1:Q0)dec |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 2 | 1 | 0 | 2 |

| 3 | 1 | 1 | 3 |

| 4 | 0 | 0 | 0 |

可以继续添加触发器(反向输出需作為触发器自己的输入),并使用前一个触发器的输出作为时钟信号。结果称作纹波计数器,可以计数到2n - 1其中n为计数器的位数(触发器的级数)。纹波计数器會受到级与级之间溢出“纹波”的不稳定输出的影响,但纹波计数器常常應用在時脈訊號除頻的應用上。一位的异步计数器可以輸入一個时钟信号,輸入一個頻率為一半的时钟信号。二位的异步计数器可以輸入一個頻率為四分之一的时钟信号……越多位的计数器其除頻比率就更高,在此應用下,瞬時的計數值不是主要考量,而整體除頻的比率才是重點。

因為用触发器的輸出作為時鐘,因此計數的資料位元之間會有时钟偏移,也因此异步计数器的技術無法和標準的同步電路設計相容。

同步计数器

在同步计数器中,所有触发器的时钟输入端连接在一起,由输入脉冲触发。因此,所有的触发器的状态同时改变(并行)。下面的电路是一个4位同步计数器。FF0的J和K输入接高电平。FF0的输出接FF1的J和K输入,FF0与FF1输出經過AND閘後連接到FF2的J和K输入,FF0、FF1与FF2输出输出經過AND閘後連接到FF3的J和K输入(右圖中是FF2的J输入和FF2的輸出,兩者在邏輯上是等價的)。接与门的输出接收的反馈。若各触发器以遞增方式編號,簡單實現此線路的方式就是讓每一個触发器在編號較小的触发器全部為高電位時反相(這也是右圖中所描述的情形)。例如位元1在位元0為高電位時反相,位元2在位元0和1均為高電位時反相,位元3在位元0,1,2均為高電位時反相……。

一般以硬體為基礎的計數器是以此架構進行。同步计数器也可以用硬體的有限状态机實現,其架構比較複雜,但可以進行更平滑,更穩定的轉態。

十进制计数器

十進制計數器是用十進制計數的計數器,可能是用二進碼十進數(BCD)計數,就像7490 IC所作的一樣,或是用其他的編碼方式(如加三碼)。

十進制計數器的每個位數需要數0到9,然後復歸到0,一般的二進制四位數計數器可以數十進制的一位數字,若是用二進碼十進數的計數方式,只要像右圖一樣加入NAND閘,其輸入為FF2及FF4,輸出為每個閘的CLR輸入即可。在每一個脈波信號時,計數器會加1,當加到二進制1010(十進制的10時),將所有的閘都清除為零,此信號經過處理後也是進位信號,表示已經算到十了。

环形计数器

环形计数器是循環的移位寄存器[2],其中的觸發器中只有一個是高電位輸出,其餘的都是低電位輸出。移位寄存器是由触发器層疊而成,若將最後一個触发器的輸出接到第一個触发器的輸入,形成一個環,即為环形计数器。

一般來說,环形计数器中循環的資料是只有一個位元為1的資料,因此任一時刻只有一個觸發器輸出為高電位。例如四位元的环形计数器,其初始狀態為1000,之後會是0001,0010,0100,1000……等。n位元的环形计数器會循環n次,每計數一次的漢明距離是2。

约翰逊记数器

约翰逊记数器(Johnson counter)也稱為尾端切換環形計數器(switchtail ring counter)、扭環計數器(twisted-ring counter)、走動環狀記數器(walking-ring counter)或莫比斯計數器(Moebius counter)是修改過的環形計數器,最後一個正反器的輸出反相後再接到第一個正反器[3][4][5]。n位元的环形计数器會循環2n次,例如例如四位元的环形计数器,其初始狀態為0000,之後會是1000, 1100, 1110, 1111, 0111, 0011, 0001, 0000, ……等。每計數一次的漢明距離是1。

约翰逊记数器可以用D型正反器或是JK正反器組合,可以用在像數位類比轉換器之類的應用。

計算機科學中的計數器

在可计算性理论中,計數器被視為是一種記憶體,可以儲存一個自然数,一般從0開始,可以到任意長度。計數器一般會和有限状态机(FSM)一起考慮,可以進行以下的步驟:

- 判斷計數器是否為零

- 計數器加一

- 計數器減一,若已經為零,計數器不變化。

以下的状态机是以其功能來排序,前面的功能比後面的強:

- 有二個計數器的确定型或非确定型有限状态机

- 加上一個堆栈的非确定有限状态自动机

- 加上一個計數器的非确定有限状态自动机

- 加上一個計數器的确定有限状态自动机

- 沒有計數器或堆栈的确定型或非确定型有限状态机

針對第一個或是最後一個,有限状态机可以是确定型,也可以是非确定型。前二者及最後一個是依喬姆斯基譜系排列。

上述的第一種有限状态机,也就是有二個計數器的有限状态机,其計算能力和图灵机等效。

網頁計數器

網頁計數器是一個電腦程式,可以顯示特定網頁瀏覽的次數。在設定後,只要有网页浏览器連結到此網頁,網頁計數器就會加一。

網頁計數器一般會用数字图像或是純文字顯示,也可能以早期的機械計數器方式顯示。圖案可以用不同的字型顯示,也可以用不同的風格,像是類似里程表的顯示方式。

網頁計數器在1980年代及1990年代相當流行,後來已被更多細節及更複雜的網站流量量測所取代。

以電腦為基礎的計數器

許多自動化系統用電腦或是手提電腦來監控機器的各種參數,並且產生資料。計數器可以計數資料,例如製作的工作數、生產批號、計算使用材料的數量等。

機械計數器

.jpg.webp)

在發明電子設備之前,就已經用機械式的計數器,像手揿号码计数器即為一例。機械式計數器一般是由幾個接在同一個軸上的轉盤組成,轉盤上有一到九的數字,每有一個事件,最右側轉盤都會加一。最左側以外的其他轉盤側面都有突起處,在旋轉一圈,。會讓左側的轉盤進行一格。像腳踏車或是汽車上用的里程表就有這類計數器,像磁帶錄音機及加油機中也有。Veeder-Root公司是機械計數器的大廠商之一,因此公司的名稱有時也用做此計數器的名稱[6]。

在資料處理產業的早期,機械計數器也用在製表機中來計算總和。

参见

- 時間-數位轉換器

- 步伐計數珠

- 日內瓦驅動器

- 念珠

- 蓋格計數器

参考文献

- , , Play hookey, [2015-05-06], (原始内容存档于2010-01-07).

- 邓元庆、关宇、贾鹏、石会. . 北京: 清华大学出版社. : 133. ISBN 978-7-302-21406-9 (中文(中国大陆)).

- Singh, Arun Kumar. . New Age Publishers. 2006 [2015-05-06]. ISBN 81-224-1759-0. (原始内容存档于2014-07-24).

- Horowitz, Paul; Hill, Winfield. . Cambridge University Press. 1989 [2015-05-06]. ISBN 0-521-37095-7. (原始内容存档于2014-07-24).

- Graf, Rudolf F. . Newnes. 1999 [2015-05-06]. ISBN 0-7506-9866-7. (原始内容存档于2014-07-24).

- , Veeder, [2015-05-06], (原始内容存档于2012-09-12).