| Unibus | |

Unibus backplane (left) and two expansion cards | |

| Year created | 1969 |

|---|---|

| Created by | Digital Equipment Corporation |

| Width in bits | 18 address, 16 data |

| Style | Parallel |

The Unibus was the earliest of several computer bus and backplane designs used with PDP-11 and early VAX systems manufactured by the Digital Equipment Corporation (DEC) of Maynard, Massachusetts. The Unibus was developed around 1969 by Gordon Bell and student Harold McFarland while at Carnegie Mellon University.[1]

The name refers to the unified nature of the bus; Unibus was used both as a system bus allowing the central processing unit to communicate with main memory, as well as a peripheral bus, allowing peripherals to send and receive data. Unifying these formerly separate busses allowed external devices to easily perform direct memory access (DMA) and made the construction of device drivers easier as control and data exchange was all handled through memory-mapped I/O.[2]

Unibus was physically large, which led to the introduction of Q-bus, which multiplexed some signals to reduce pin count. Higher performance PDP systems used Fastbus, essentially two Unibusses in one. The system was later supplanted by Massbus, a dedicated I/O bus introduced on the VAX and late-model PDP-11s.

Technical specifications

The Unibus consists of 72 signals, usually connected via two 36-way edge connectors on each printed circuit board. When not counting the power and ground lines, it is usually referred to as a 56-line bus. It can exist within a backplane or on a cable. Up to 20 nodes (devices) can be connected to a single Unibus segment; additional segments can be connected via a bus repeater.

The bus is completely asynchronous, allowing a mixture of fast and slow devices. It allows the overlapping of arbitration (selection of the next bus master) while the current bus master is still performing data transfers. The 18 address lines allow the addressing of a maximum of 256 KB. Typically, the top 8 KB is reserved for the registers of the memory-mapped I/O devices used in the PDP-11 architecture.

The design deliberately minimizes the amount of redundant logic required in the system. For example, a system always contains more slave devices than master devices so most of the complex logic required to implement asynchronous data transfers is forced into the relatively few master devices. For interrupts, only the interrupt-fielding processor needs to contain the complex timing logic. The result is that most I/O controllers can be implemented with simple logic, and most of the critical logic is implemented as a custom MSI IC.

Pinout

| Number | Name | Type | Description |

|---|---|---|---|

| 18 | A00-A17 | 1 | Address Lines |

| 16 | D00-D15 | 1 | Data Lines |

| 4 | BR4-BR7 | 1 | Bus (Interrupt) Requests at priorities 4 (lowest) through 7 (highest) |

| 4 | BG4-BG7 | 2 | Bus (Interrupt) Grants at priorities 4 (lowest) through 7 (highest) |

| 1 | NPR | 1 | Non Processor (DMA) Request |

| 1 | NPG | 2 | Non Processor (DMA) Grant |

| 1 | MSYNC | 1 | Master Sync |

| 1 | SSYNC | 1 | Slave Sync |

| 1 | BBSY | 1 | Bus Busy |

| 1 | SACK | 1 | Selection Acknowledge |

| 1 | INIT | 1 | Bus Init |

| 1 | INTR | 1 | Interrupt Request |

| 1 | PA | 1 | Parity control |

| 1 | PB | 1 | Parity control |

| 2 | C0-C1 | 1 | Control Lines |

| 1 | ACLO | 3 | AC Low |

| 1 | DCLO | 3 | DC Low |

| 2 | +5v | - | Power Lines (not counted as part of the 56) |

| 14 | Gnd | - | Ground Lines (not counted as part of the 56) |

Type 1 lines are a normal multi-sender wired-OR bus with pull-up resistors at each end of the bus, typically on a terminator card.[3]

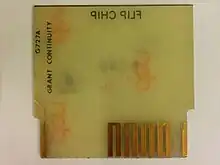

Type 2 lines are selectively propagated by each card to the next slot – if the card wants to keep the request grant it will assert the SACK line and not propagate the request to the next slot. If a slot is empty, it is necessary to install a "grant continuity card" in the slot to propagate the four type 2 signals to the next card.[3]

Type 3 signals are generated by the power supply and have only a single sender. They warn the devices on the bus when the power is about to fail, so those devices can execute an orderly shutdown, and disable operations to prevent spurious writes.[3]

The two control lines (C0 and C1) allowed the selection of four different data transfer cycles:

- DATI (Data In, a read)

- DATIP (Data In/Pause, the first portion of a Read-Modify-Write operation. A DATO or DATOB operation completes this.)

- DATO (Data Out, a word write)

- DATOB (Data Out/Byte, a byte write)

- During an interrupt cycle, a fifth style of transfer was automatically invoked to convey an interrupt vector from the interrupting device to the interrupt-fielding processor.

References

- ↑ Gardner Hendrie, Interviewer (June 23, 2005). "Bell (Gordon) Oral History". Reference number: X3202.2006. Computer History Museum. Retrieved May 20, 2011.

{{cite web}}:|author=has generic name (help) - ↑ "PDP-11 Buses". University of Sydney.

- 1 2 3 Digital Equipment Corporation (1979). "Unibus Specification" (PDF).