同或门

同或门(英語:,偶尔写作、,在Intel處理器中,此项功能被命名為"test"),又称异或非门,是数字逻辑中实现逻辑双条件的逻辑门,功能见右侧真值表。若两个输入的电平相同,则输出为高电平(1);若两个输入的电平相异,则输出为低电平(0)。

| 基本逻辑閘 | |

| 緩衝 | 非 |

| 或 | 或非 |

| 异或 | 同或 |

| 蘊含 | 蘊含非 |

| 输入 A B | 输出 A XNOR B | |

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

概述

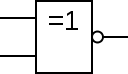

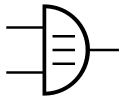

下列包括逻辑门的3种符号:形状特征型符号(ANSI/IEEE Std 91-1984)、IEC矩形国标符号(IEC 60617-12)和不再使用的DIN符号(DIN 40700)。其他的逻辑门符号见逻辑门符号表。

| 表达式 | 符号 | 功能表 | 继电器逻辑 | ||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| ANSI/IEEE Std 91-1984 | IEC 60617-12 | DIN 40700 | |||||||||||||||||||||||

|

|

或  |

|

| |||||||||||||||||||||

等价於。

硬件描述和引脚分配

同或门是基本的逻辑门,因此在TTL和CMOS集成电路中都是可以使用的。标准的4000系列CMOS集成电路为4077,包含四个独立的2输入同或门。引脚分配如下:

74266四同或门DIP封装集成电路的引脚分配图 |

|

包括NXP在内的很多半导体制造商都生产这一元件,封装方式分为直插DIP封装和SOIC封装两种。元件的資料表可在大多数元件数据库查询到。

备选方案

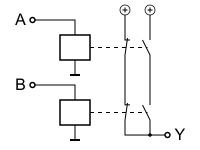

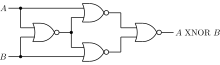

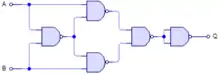

如果没有现成的同或门,我们可利用四个或非门或五个与非门来实现,连线方法见下图。因为与非门和或非门是“通用的门电路”,因此任何一个逻辑函数都可单独由与非逻辑或或非逻辑来实现。

仅用或非门实现的同或门 |

仅用与非门实现的同或门 |

参考文献

This article is issued from Wikipedia. The text is licensed under Creative Commons - Attribution - Sharealike. Additional terms may apply for the media files.