緩衝閘

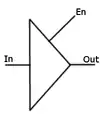

緩衝閘[1](英語:)又稱、同閘、是閘(英語:)[2]、驅動器或放大器,是一種會輸出一個與輸入相同邏輯訊號的邏輯閘,是數位邏輯中實現緩衝或放大用的邏輯閘,也可使當成數位邏輯中實現邏輯命題的邏輯閘,功能見右側真值表。

| 基本逻辑閘 | |

| 緩衝 | 非 |

| 或 | 或非 |

| 异或 | 同或 |

| 蘊含 | 蘊含非 |

| 輸入 A | 輸出 BUF(A) |

| 0 | 0 |

| 1 | 1 |

雖然直接複製輸入爲輸出似乎是一件毫無意義的事情,它也有實際的應用,例如一個微弱的信號源可以透過緩衝閘而增強訊號[3]。緩衝閘前後的邏輯電平是不變的,因此有時也作為數位中繼器[4]。

緩衝閘與直接導通不同,緩衝閘與其他邏輯閘一樣都有延遲,因此緩衝閘有時被做為數位電路的訊號延遲元件[5]。

緩衝閘是一種單一輸入邏輯閘,另外一種單一輸入邏輯閘是反相器,功能正好相反。

概述

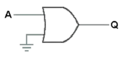

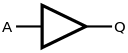

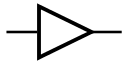

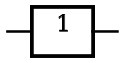

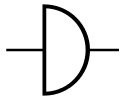

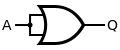

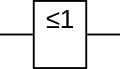

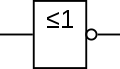

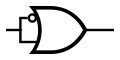

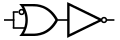

下列包括邏輯閘的3種符號:形狀特徵型符號(ANSI/IEEE Std 91-1984)、IEC矩形國標符號(IEC 60617-12)和不再使用的DIN符號(DIN 40700)。其他的邏輯閘符號詳見逻辑门符号表。

| 表達式 | 符號 | 功能表 | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| ANSI/IEEE Std 91-1984 | IEC 60617-12 | DIN 40700 | ||||||||

|

|

|

| |||||||

性質

因為緩衝閘的輸出端訊號等於輸入端訊號,所以它並不會執行任何邏輯運算功能。但在數位電路中有時會需要使用緩衝閘來增加訊號強度,例如有一個邏輯閘的扇出數為4[註 1],但是該邏輯電路需要將其輸出再接到超過五個邏輯閘,此時可以在中間串接一個緩衝閘,由於緩衝閘不會使電路的邏輯行為發生改變,因此此舉可以確保電路的邏輯行為正確無誤。另外在單純NMOS或PMOS的邏輯電路中也可以使用緩衝閘來減少PMOS對高電平的電壓降與NMOS對低電平的電壓升。

此外由於邏輯閘運作時都會有延遲,但緩衝閘不會執行任何邏輯運算功能,因此也可以做為電路中訊號延遲的元件。

電路實現

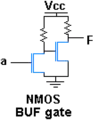

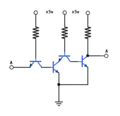

NMOS緩衝閘

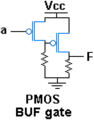

NMOS緩衝閘 PMOS緩衝閘

PMOS緩衝閘 TTL緩衝閘

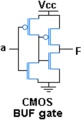

TTL緩衝閘 靜態CMOS緩衝閘

靜態CMOS緩衝閘

緩衝閘電路輸出電壓所代表的邏輯電平與輸入相同,這剛好與反相器相反,由於邏輯對合律,因此緩衝閘可由兩個反相器組合而成,反相器可以僅用一個NMOS電晶體或一個PMOS連接一個電阻來構建,因此緩衝閘也可以使用串接的兩個NMOS電晶體或PMOS電晶體構成,而CMOS則是將這兩種加以組合,達到互補的效果。

積體電路

六同相器是一種包含6個緩衝閘的積體電路。例如,7407 TTL晶片有14個引腳,4050 CMOS晶片有16個引腳,兩種晶片都各有2個引腳用於電源供電/基準電壓,12個引腳用於6個緩衝閘的輸入和輸出(4050有2個引腳懸空)[6]。此外,741G34也是一種緩衝閘[7],但裡面只有單一個緩衝閘。

備選方案

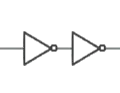

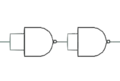

利用反相器實現的緩衝閘

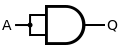

利用反相器實現的緩衝閘 利用及閘實現的緩衝閘

利用及閘實現的緩衝閘 利用或閘實現的緩衝閘

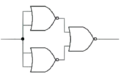

利用或閘實現的緩衝閘 利用反及閘實現的緩衝閘

利用反及閘實現的緩衝閘 利用反或閘實現的緩衝閘

利用反或閘實現的緩衝閘

緩衝閘只要是邏輯輸出等於邏輯輸入的組合皆能使用,但不能使用電線代替,有些情況可以先用電壓跟隨器代替,但可能會有潛在的問題,最安全的方式是將兩個反相器串接。

由於緩衝閘要實現的等同於邏輯命題,因此只要輸入與輸出相等的函數皆能使用,例如邏輯的:冪等律、有界律、對合律與吸收律。

| 幂等律 | ||

| 有界律 | ||

| 對合律 | ||

| 吸收律 |

最簡單的兩種方式是將或閘或與閘的兩個輸入接在一起即可完成一個緩衝閘[8]。另外,也能使用被認為是「通用的邏輯閘電路」的反及閘與反或閘[9]來實現。若用反及閘實現緩衝閘,則將兩個反及閘的兩個輸入接在一起,然後將之串接;若用反或閘實現緩衝閘,則將兩個反或閘的四個輸入接在一起作為輸入,然後將兩個輸出接在第三個反或閘的兩個輸入即完成一個緩衝閘。

三態邏輯運用

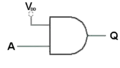

一般邏輯閘輸出的高電位大部分是使用VDD端接高電位或電源而完成,但若將緩衝閘的VDD端接也作為輸入的話則可以達成三態邏輯的效果[10]。 這個效果則允許輸出端在0和1兩種邏輯電平之外呈現高阻態,等效於將輸出的影響從後級電路中移除。這允許多個電路共同使用同一個輸出線(例如匯流排)。

| 輸入 A B | 輸出 C | |

| 0 | 1 | 0 |

| 1 | 1 | |

| X | 0 | Z |

單一輸入邏輯閘

緩衝閘是一種單一輸入邏輯閘,另外一種單一輸入邏輯閘是反相器。在布林代數中,單一輸入的布林函數共有四種:

其中兩種就是緩衝閘與反相器,分別實現邏輯命題與邏輯非,而另外兩種分別為邏輯永真以及邏輯永假。

| 邏輯閘 | 邏輯命題 | 邏輯非 | 邏輯永真 | 邏輯永假 |

| 緩衝閘 | 相反閘 | 恆真閘 | 恆假閘 | |

| 輸入 A | 輸出 BUF(A) | 輸出 |

輸出 永真 | 輸出 永假 |

| 0 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

恆真閘的IEC記號

恆真閘的IEC記號 恆假閘的IEC記號

恆假閘的IEC記號 蘊含閘組成的恆真閘

蘊含閘組成的恆真閘

但在數位邏輯電路中通常不會出現恆真閘與恆假閘,因為恆真閘實際上就是指短路、電源或高電位(邏輯真)的供應元件,反之恆假閘就是指斷路或接地,且這兩種的輸出與輸入無關。

註釋

- 輸出端可接的標準負載個數的最大值

參考文獻

- buffer gate (页面存档备份,存于) terms.naer.edu.tw 國家教育研究院 2003-6 [2015-10-1]

- YES gates (页面存档备份,存于) 2012.igem.org [2015-10-1]

- Buffer gate (页面存档备份,存于) logic.ly [2015-10-1]

- The “Buffer” Gate (页面存档备份,存于) allaboutcircuits.com [2015-10-1]

- Logic gates (页面存档备份,存于) 章節1:Inverter (NOT Gate) and Buffer, 第二部分:Buffer Gate, macao.communications.museum [2015-10-1]

- Texas Instruments:4050b CMOS六同相緩衝器/轉換器 (页面存档备份,存于),資料表:CMOS Hex Buffer/Converters (页面存档备份,存于)

- 741G34(SN74LVC1G34)的資料表 (页面存档备份,存于) ti.com [2015-10-1]

- logic gate (页面存档备份,存于) 段落 YES gate, cpuville.com [2015-10-1]

- Mano, M. Morris and Charles R. Kime. Logic and Computer Design Fundamentals, Third Edition. Prentice Hall, 2004. p. 73.

- Tri-state use buffer gate (页面存档备份,存于) lectronics-tutorials.ws [2015-10-1]