皮爾斯振盪器

皮爾斯振盪器()或稱皮爾斯晶體振盪器,是一種電子振盪電路,特別適用於配合石英振盪晶體以產生振盪訊號。得名於發明者:喬治·皮爾斯(,1872-1956。[1][2]

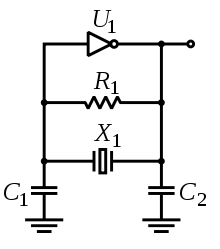

皮爾斯振盪器衍生自考畢子振盪器。現今使用石英晶體進行振盪以產生時鐘訊號的數位電路,幾乎均使用皮爾斯振盪器電路,因為它電路簡單,工作有效而穩定,優於其它型態的石英晶體振盪電路。皮爾斯振盪器所需零件很少:一個反相器、一個電阻、一個石英晶體、兩個小電容。石英晶體在此扮演高選擇度的濾波元件。此外,很多 IC 已內建反相器與電阻,只要在外部加上石英晶體與兩個電容就可以工作。由於石英晶體頻率穩定,此電路成本又很低,因此廣泛用於各種消費電子產品之中。

工作原理

偏壓電阻

回授電阻 R1 可以看成是反相器的偏壓電阻,令反相器工作在線性區域而成為高增益的反相放大器,並確保振盪的發生。

不妨這樣看: 假設此反相器為理想反相器,輸入阻抗無限大、輸出阻抗為0,則此電阻將令輸入電壓與輸出電壓相等,因而使反相器內的電晶體不會工作在完全導通或完全截止的狀態,而是工作在具有增益的中間過渡區域。

共振器

石英晶體與 C1, C2 兩電容構成π型網路形式的帶通濾波器,約在石英晶體的共振頻率上,提供 180 度相移與所需的電壓增益。

在發生振盪的頻率上,石英晶體呈現電感性,可視為是具有高 Q 值的電感。π型網路的 180 度相移加上反相器的負增益,合起來成為正的環增益(正回授),使 R1 所設定的偏壓無法穩定而導致振盪。

隔離電阻

有時會在反相器的輸出與石英晶體與電容的π型網路間,額外串入一個電阻,把輸出與π形網路隔離開來。此電阻會與 C2 造成些許額外的相移。[3]

加入這個電阻的主要目的有:

- 抑制高頻混附(spurious)振盪,以獲得乾淨的輸出訊號。

- 降低石英晶體的驅動功率,以防止超過石英晶體的容許驅動功率(術語稱驅動準位,)而加速老化或造成破損,尤其是對低功率的石英晶體。

負載電容

由石英晶體看出去,電路上的總電容量稱為石英晶體的「負載電容」。由於負載電容量對電路所振盪出的訊號頻率有些影響,因此,石英晶體的規格中會寫明負載電容的數值,規格書中的振盪頻率,是以符合此負載電容值的電路為準。

因此,為達到正確的振盪頻率,電路設計者應確保電路上的負載電容符合石英晶體的負載電容規格。在計算負載電容時,電路的雜散電容,例如電路板銅箔間的電容,IC 接腳的電容等,均需納入考慮。

參見

參考資料

- George W. Pierce (October 1923) "Piezoelectric crystal resonators and crystal oscillators applied to the precision calibration of wavemeters," Proceedings of the American Academy of Arts and Sciences, vol. 59, no. 4, pages 81-106.

- George W. Pierce, "Electrical System," U.S. patent 2,133,642 (filed: 25 February 1924; issued: 18 October 1938). Available on-line at: http://patimg1.uspto.gov/.piw?Docid=02133642&homeurl=http%3A%2F%2Fpatft.uspto.gov%2Fnetacgi%2Fnph-Parser%3FSect1%3DPTO1%2526Sect2%3DHITOFF%2526d%3DPALL%2526p%3D1%2526u%3D%25252Fnetahtml%25252FPTO%25252Fsrchnum.htm%2526r%3D1%2526f%3DG%2526l%3D50%2526s1%3D2,133,642.PN.%2526OS%3DPN%2F2,133,642%2526RS%3DPN%2F2,133,642&PageNum=&Rtype=&SectionNum=&idkey=NONE&Input=View+first+page .

- Fairchild Semiconductor Corporation, HCMOS Crystal Oscillators: Fairchild Semiconductor Application Note 340, May 1983, pp. 1-2PDF (45.4 KiB)