反相器

反相器(英語:)也称非门(英語:),是数字逻辑中实现逻辑非的逻辑门,功能见右侧真值表。

| 基本逻辑閘 | |

| 緩衝 | 非 |

| 或 | 或非 |

| 异或 | 同或 |

| 蘊含 | 蘊含非 |

| 输入 A | 输出 NOT A |

| 0 | 1 |

| 1 | 0 |

这种功能代表了数字电路中理想开关表现的假定,但是在实际的反相器设计中,元件有其需要特别关注的电气特性。实际上,CMOS反相器的非理想过渡区表现使其能在模拟电路中用作A类功率放大器(如作为运算放大器的输出级[1])。

概述

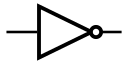

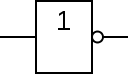

下列包括逻辑门的3种符号:形状特征型符号(ANSI/IEEE Std 91-1984)、IEC矩形国标符号(IEC 60617-12)和不再使用的DIN符号(DIN 40700)。其他的逻辑门符号见逻辑门符号表。

| 表达式 | 符号 | 功能表 | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| ANSI/IEEE Std 91-1984 | IEC 60617-12 | DIN 40700 | ||||||||

|

|

|

| |||||||

电路实现

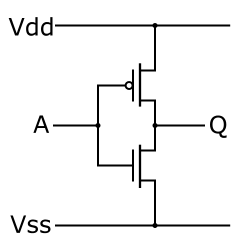

NMOS反相器

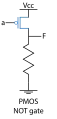

NMOS反相器 PMOS反相器

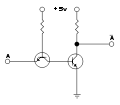

PMOS反相器 TTL反相器

TTL反相器 静态CMOS反相器

静态CMOS反相器 饱和负载数字反相器

饱和负载数字反相器.png.webp) 三极管反相器

三极管反相器 开关实现的反相器

开关实现的反相器

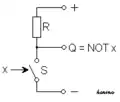

反相器电路输出电压所代表的逻辑电平与输入相反。反相器可以仅用一个NMOS晶体管或一个PMOS连接一个电阻来构建。因为这种“阻性漏极”方式只需要使用一种类型的晶体管,其制造成本非常小。不过,由於电流以两种状态之一流过电阻,这种阻性漏极配置有功耗和状态改变的处理速率问题。另外,反相器可以用两个互补晶体管配置成CMOS反相器。这种配置可以大幅降低功耗,因为在两种逻辑状态中,两个晶体管中的一个总是截止的。处理速率也能得到很好的提高,因为与NMOS型和PMOS型反相器相比,CMOS反相器的电阻相对较低。反相器也可以电阻-晶体管逻辑(RTL)或晶体管-晶体管逻辑(TTL)使用双极性晶体管(BJT)构建。

數碼电子电路在逻辑0和1(二进制)对应的固定电压电平范围内进行运算。反相器电路是基本的逻辑门,可以在两个电压电平间变换。实际构建的反相器的电压都是不同的,例如TTL电路中0是低电平,+5V是高电平。

数字功能模块

反相器是数字电路中的一种基本功能模块。将两个串行反相器的输出作为一位寄存器的输入就构成了锁存器。锁存器、数据选择器、译码器和状态机等精密数字元件都需要使用基本反相器。

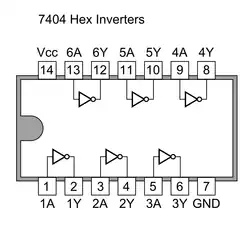

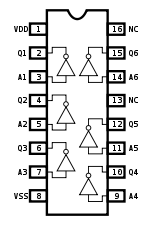

六反相器是一种包含6个反相器的集成电路。例如,7404 TTL芯片有14个引脚,4049 CMOS芯片有16个引脚,两种芯片都各有2个引脚用於电源供电/基准电压,12个引脚用於6个反相器的输入和输出(4049有2个引脚悬空)。[2]

性能测定

反相器性能常用表示输入-输出电压关系的电压传输特性曲线(VTC)来测定。曲线图能反映出元件的参数,包括噪声容限、增益和操作逻辑电平。

反相器理想化的电压传输特性曲线是单位阶跃函数,这表明反相器能在高电平和低电平间无延迟精确的翻转,但在实际元件中,曲线存在过渡区。曲线表明若输入为低电压,则输出为高电压;若输入为高电压,则输出电压逐渐接近0V。过渡区的斜率是性能测量的指标,过渡区越陡峭,即斜率越大,性能越好,若斜率接近无穷,则电路能在高电平和低电平间精确翻转,反相器就是理想的。

噪声容限可以通过每一工作区中的最大输出电压VOH和最小输入电压VIL的比值来测定。

输出电压VOH可以在级联多个元件时测定信号驱动强度。

參考文獻

- Intersil数据表:CA3130 BiMOS运算放大器 (页面存档备份,存于)和CA3160 BiMOS运算放大器 (页面存档备份,存于)

- Texas Instruments:4049 CMOS六反相缓冲器/转换器 (页面存档备份,存于),数据表: (页面存档备份,存于)

| 维基共享资源上的相关多媒体资源:反相器 |