Intel Tick-Tock

Tick-Tock是Intel公司發展微處理器晶片設計製造業務的一種發展戰略模式,在2007年正式提出。Intel指出,每一次處理器微架構的更新和每一次晶片製程的更新,它們的時機應該錯開,使他們的微處理器晶片設計製造業務更有效率地發展。“Tick-Tock”的名稱源於時鐘秒針行走時所發出的聲響。Intel指,每一次“Tick”代表著一代微架構的處理器晶片製程的更新,意在處理器效能幾近相同的情況下,縮小晶片面積、減小能耗和發熱量;而每一次“Tock”代表著在上一次“Tick”的晶片製程的基礎上,更新微處理器架構,提升效能。一般一次“Tick-Tock”的週期為兩年,“Tick”佔一年,“Tock”佔一年。[1]

此策略常被許多電腦玩家戲稱“擠牙膏策略”,因為每一代新處理器效能和前一代處理器效能的差距很短,就好像Haswell的4790K和Skylake的6700K那樣。2016年3月22日,Intel在财务报告中宣布放弃Tick-Tock,改用增加优化环节的制程-架构-优化模型。[2]

Intel的主要對手AMD歷年來也跟隨著Intel的製程腳步做處理器演進,並在2009年於美國分拆出子公司格羅方德作為代工夥伴,一直合作生產直到2018年14奈米的Zen處理器產品為止。由於製程難度提高,AMD在2018年8月底公佈消息,取消以格羅方德做為Zen2處理器產品代工夥伴的規劃,轉用台積電作為代工廠以生產7奈米的Zen2處理器,而此時的Intel之10奈米產線仍因為良率問題無法大規模供貨於市場。AMD在2019年11月底宣布,將會繼續遵循Intel Tick Tock的精神繼續生產Zen2及Zen3處理器。

[3]

環節

2016年以前,英特尔仍使用Tick-Tock。

Tick:更新处理器芯片制程。

Tock:更新处理器架构,提升能效比和IPC。

2016年后,Intel已放弃Tick-Tock,改用增加优化环节的制程-架构-优化模型。

目前的環節為:Process, Architecture, Optimization,即製程、架構、優化

製程:在架構不變的情況下,縮小電晶體體積,以減少功耗及成本

架構:在製程不變的情況下,更新處理器架構,以提高性能

優化:在製程及架構不變的情況下,進行修復及優化,將BUG減到最低,並提升處理器時脈

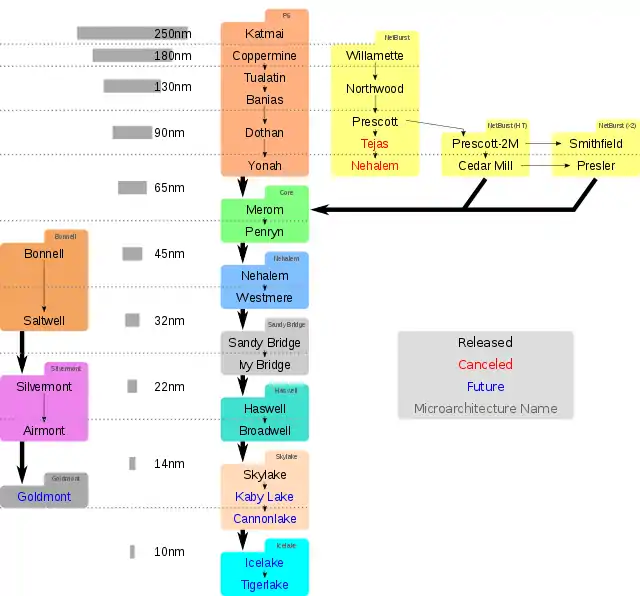

產品發布路線圖

| 微架構更新 | 微架構 | 製造工藝/製程 | 發佈時間 | 處理器 | ||||||

|---|---|---|---|---|---|---|---|---|---|---|

| 八路/四路伺服器平台 處理器核心代號 |

四路/雙路伺服器/工作站平台 處理器核心代號 |

極致效能/工作站平台 處理器核心代號 |

主流桌面平台 處理器核心代號 |

流動平台 處理器核心代號 |

處理器品牌 | |||||

| Tick | 製程 | Presler, Cedar Mill, Yonah | 65納米 | 2006年1月5日 | Presler | Cedar Mill | Yonah | |||

| Tock | 架構 | Core | 2006年6月27日[4] | Kentsfield | Conroe | Merom | ||||

| Tick | 製程 | Penryn | 45納米 | 2007年11月11日[5] | Dunnington | Harpertown | Yorkfield | Wolfdale | Penryn | |

| Tock | 架構 | Nehalem | 2008年11月17日[6] | Nehalem-EX (Beckton) | Nehalem-EP (Gainestown) | Bloomfield | Lynnfield | Clarksfield | ||

| Tick | 製程 | Westmere | 32納米 | 2010年1月4日[7][8] | Westmere-EX | Westmere-EP | Gulftown | Clarkdale | Arrandale | |

| Tock | 架構 | Sandy Bridge | 2011年1月9日[9] | — | Sandy Bridge-EP | Sandy Bridge-E | Sandy Bridge | Sandy Bridge-M | ||

| Tick | 製程 | Ivy Bridge | 22納米 | 2012年4月23日 | Ivy Bridge-EX | Ivy Bridge-EP | Ivy Bridge-E | Ivy Bridge | Ivy Bridge-M | |

| Tock | 架構 | Haswell | 2013年6月4日至6月8日 | Haswell-EX | Haswell-EP | Haswell-WS | Haswell | — | ||

| Process | 製程 | Broadwell[10] | 14納米[11] | 2014年1月 | Broadwell-EP | Broadwell-E | Broadwell-C | Broadwell-H/Broadwell-U/Broadwell-Y | ||

| Architechture | 架構 | Skylake | 2015年8月5日 | Skylake-S | Skylake-H/Skylake-U/Skylake-Y | |||||

| Optimization | 優化 | Kaby Lake | 14奈米+ | 2016年8月30日 | Kaby Lake-S | Kaby Lake-H/Kaby Lake-U/Kaby Lake-Y | ||||

| Optimization | 優化 | Coffee Lake | 14奈米++ | 2017年10月5日 | Coffee Lake-S | |||||

| Process | 製程 | Cannon Lake | 10納米 | 2018年 | ||||||

| Architechture | 架構 | Ice Lake | 2019年 | |||||||

| Optimization | 優化 | Tiger Lake | 2020年 | |||||||

| Optimization | 優化 | 10奈米++ | 20xx年 | |||||||

| Process | 製程 | 7納米 | 20xx年 | |||||||

| Architechture | 架構 | 20xx年 | ||||||||

| Optimization | 優化 | 20xx年 | ||||||||

| Optimization | 優化 | 7奈米++ | 20xx年 | |||||||

參見

參考資料

- . [2012-06-06]. (原始内容存档于2017-01-07).

- Cutress, Ian. . www.anandtech.com. [2022-07-25]. (原始内容存档于2020-11-27).

- . [2019-12-18]. (原始内容存档于2019-12-18).

- Intel CEO: Latest Platforms, Processors Form New Foundations For Digital Entertainment And Wireless Computing (页面存档备份,存于), Intel Unveils World's Best Processor (页面存档备份,存于)

- . [2012-06-06]. (原始内容存档于2009-02-18).

- . [2012-06-06]. (原始内容存档于2011-12-21).

- (PDF). [2012-06-06]. (原始内容存档 (PDF)于2012-10-02).

- . [2012-06-06]. (原始内容存档于2011-06-05).

- . [2012-06-06]. (原始内容存档于2012-05-16).

- (PDF). [2012-06-06]. (原始内容存档 (PDF)于2013-07-06).